Received 7 January 2023, accepted 7 February 2023, date of publication 14 February 2023, date of current version 1 March 2023. Digital Object Identifier 10.1109/ACCESS.2023.3244902

## **RESEARCH ARTICLE**

# **ReTrustFSM: Toward RTL Hardware Obfuscation-A Hybrid FSM Approach**

M. SAZADUR RAHMAN<sup>®</sup>, RUI GUO<sup>®</sup>, HADI M. KAMALI<sup>®</sup>, FAHIM RAHMAN, FARIMAH FARAHMANDI, (Member, IEEE), AND MARK TEHRANIPOOR, (Fellow, IEEE)

Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL 32611, USA

Corresponding author: M. Sazadur Rahman (mohammad.rahman@ufl.edu)

**ABSTRACT** Hardware obfuscating is a proactive design-for-trust technique against IC supply chain threats, i.e., IP piracy and overproduction. Many studies have evaluated numerous techniques for obfuscation purposes. Nevertheless, de-obfuscation attacks have demonstrated their insufficiency. This paper proposes a register-transfer (RT) level finite-state-machine (FSM) obfuscation technique called ReTrustFSM that allows designers to obfuscate at the earliest possible stage. ReTrustFSM combines three types of secrecy: explicit external secrecy via an external key, implicit external secrecy based on specific clock cycles, and internal secrecy through a concealed FSM transition function. So, the robustness of ReTrustFSM relies on the external key, the external primary input patterns, and the cycle accuracy of applying such external stimuli. Additionally, ReTrustFSM defines a cohesive relationship between the features of Boolean problems and the required time for de-obfuscation, ensuring a maximum execution time for oracle-guided de-obfuscation attacks. Various attacks are employed to test ReTrustFSM's robustness, including structural and machine learning attacks, functional I/O queries (BMC), and FSM attacks. We have also analyzed the corruptibility and overhead of design-under-obfuscation. Our experimental results demonstrate the robustness of ReTrustFSM at acceptable overhead/corruption while resisting such threat models.

**INDEX TERMS** Hardware obfuscation, logic locking, FSM, RTL, structural analysis, BMC.

#### I. INTRODUCTION

Due to the ever-increasing costs/complexity of IC manufacturing, the rush time-to-market, and the ability to take advantage of cutting-edge technologies, many companies are adopting the horizontal model, where multiple independent entities fulfill various stages of the IC supply chain, forming a globally distributed supply chain [1]. Albeit highly beneficial, with outsourcing, the original equipment manufacturers take fewer precautions to meet the market demand (OEM). With no reciprocal trust and a lack of reliable monitoring, the control of OEMs and third-party IP vendors over the supply chain reduces drastically, resulting in numerous hardware security threats, including but not limited to IP piracy, IC overproduction, and counterfeiting [2], [3].

Many design-for-trust solutions (e.g., watermarking, IC metering, IC camouflaging, and hardware obfuscation)

The associate editor coordinating the review of this manuscript and approving it for publication was Kashif Saleem<sup>(D)</sup>.

have been studied in the literature to address these threats [4], [5], [6], [7]. Over the last two decades, hardware obfuscation, a.k.a. logic locking, has garnered considerable attention as a trustworthy proactive method for securing IP [8]. Logic locking enables the IP/IC designers to support postfabrication activation of the fabricated designs to recover the underlying functionality. The logic locking secret governs the resulting locked circuit functionality, i.e., the key, and is only known to authorized/trusted entities, e.g., IP owners or OEMs.

Since 2005 [7], numerous studies have focused on various methodologies for building sophisticated obfuscation techniques. However, with newer de-obfuscation attacks, the robustness of most locking solutions has been undermined. Functional input/output (I/O) query-based attacks that primarily rely on satisfiability (SAT) solvers [9] are widely applicable to different combinational logic locking techniques [10], [11]. Structural analysis-based attacks [12], [13], [14] on point function techniques [15], [16], [17], [18],

| Method                   | Mechanism                                                               | Vulnerability                                                                       | Exploited by                                |  |

|--------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------|--|

| HARPOON<br>[30]          | Adds extra authentication and obfuscation states prior the original FSM | Obfuscated states start first and are loosely connected to the original part of FSM | RANE [28], Fun-SAT [29],<br>Structural [31] |  |

| Interlocking [32]        | Augments orignial FSM with obfuscation mode and code-word               | Code-word doesn't impact output function                                            | Fun-SAT [29], Structural [31]               |  |

| State [33]<br>Deflection | Verifies enabling key at each state and deflects to black holes         | Obfuscated states are loosely connected to the orignial part of FSM                 | Structural [31]                             |  |

| Active [5]<br>Metering   | Adds extra obfuscation states and black holes for correct order         | Obfuscated states are loosely connected to the original FSM                         | Fun-SAT [29],<br>Structural [31]            |  |

| JANUS [34, 35]           | Concealment state register role using a configurable FF                 | Leaves scan chain open (leak of FF type)                                            | BMC not tested (§II-D)                      |  |

#### TABLE 1. Comparison of ReTrustFSM with the existing FSM obfuscation methods.

attacks relying on machine learning [19], [20] on routing-based techniques [21], [22], [23], and theory-based SAT attacks [24], [25] on non-Boolean logic locking [26], [27] are some of the evident examples showing the concerning state of the logic locking.

Logic locking can be categorized into *combinational* and *sequential*. Combinational locking targets the combinational functions (logic parts) [10], [11], [15], [16], [17], [18], [21], [22], [23], [26], [36], whereas sequential ones target the state transitions graphs (STG) of the circuits [28], [30], [31], [32], [33], [34], [35], [37], [38], [39], [40]. In almost all sequential logic locking techniques, instead of having a dedicated reference (secret) as the key (i.e., explicit external secrecy), a sequence of input patterns serves as the unlocking/activation condition (i.e., implicit external secrecy). So, combinational locking is also known as key-based, while sequential logic locking is a keyless one.

Over time, many keyless locking methods have been challenged by different techniques [29], [31], [41]. The {structural+functional} attack focuses on the topological flaws of these methods that allow the adversary to distinguish the original part of the STG from the obfuscated part, leading to recovering the correct FSM [31], [38]. More recent approaches show how these keyless locking, even while they are utilizing implicit representation of the secret [30], [32], [33], [34], [35], [37], can be remodeled and evaluated using I/O query-based attacks like the BMC attack [29], [41]. Table 1 shows a comparative summary of the notable FSM obfuscation methods, their vulnerabilities, and the attacks they are susceptible to (discussed in Sec. II-D).

This paper proposes a novel FSM-based logic locking, called **ReTrustFSM** that targets multiple forms of threats against logic locking. ReTrustFSM is an effort of logic locking at the RTL that leverages the behavioral state transition coding for obfuscation. In ReTrustFSM, both keyless (implicit external secrecy) and key-based (explicit external secrecy) types of locking have been utilized with a high correlation that boosts the robustness of the solution, against oracle-guided I/O query-based attacks and {structural+functional} attack. Also, ReTrustFSM formulates (models) the relationship between Boolean features and

the expected de-obfuscation time. By using such a model, ReTrustFSM can be configured in a way that guarantees the targeted time. Additionally, by revealing the leakage possibility of a recent study on FSM-based obfuscation, we evaluate the requirements of the design-for-testability (DFT) structure (scan chain architecture) obfuscation once the FSM-based obfuscation is in place. Our main contributions are as follows:

(1) RT-Level FSM Obfuscation: In ReTrustFSM, the STG is extracted and obfuscated at RT-level.

(11) FSM Re-Encoding Via Explicit External Secrecy: ReTrustFSM uses a counter and LFSR-based FSM obfuscation technique tightly coupled with the original FSM, where the external secrecy (the key) determines how intermediate FSM states (and their encoding values) become dependent on the value/status of the counter/LFSR.

(III) FSM (In-the-Middle) Obfuscation Via Implicit External Secrecy: We utilize a keyless FSM obfuscation technique that conceals intermediate state transition functioning to boost the robustness by building deep obfuscation-oriented transitions directly dependent on the input patterns in a cycleaccurate manner.

(*IV*) Evaluation of Circuit Attributes for FSM Obfuscation: We equipped ReTrustFSM with an ML-based analysis that focuses on the core features of the obfuscated circuit. The benefit of such a mechanism is twofold: (a) It boosts the complexity of the obfuscated circuit against the existing attacks, particularly I/O query-based attacks, and (b) ReTrustFSM becomes capable of targeting the desired de-obfuscation time before configuring the obfuscation parameters and building the obfuscated circuit(s).

(V) Comprehensive Security/PPA Analysis: To show the comprehensiveness and robustness of the proposed approach, we conduct different analyses using a wide variety of stateof-the-art attacks on the proposed logic locking.

The rest of the paper is organized as follows: Section II covers backgrounds of key-based and keyless obfuscation, as well as FSM obfuscation. Section III provides the details of the proposed scheme. Detailed security analysis of ReTrustFSM is discussed in Section IV. Section V demonstrates the efficiency of ReTrustFSM experimentally. Finally, Section VI concludes the paper.

## II. BACKGROUND

## A. THREAT MODEL

FSM-based de-obfuscation attacks are considered successful if the adversary can (1) separate the original STG from the obfuscated part, or (2) retrieve external secrets (explicit/implicit), allowing reconstruction of the original STG. In de-obfuscation attacks, the threat model defines the adversary's capability at the time of the attack. This work considers the following assumptions for threat modeling [9]:

## 1) ADVERSARY DEFINITION

Any individual involved in the IC lifecycle, from the untrusted foundry to malicious end-users, can be an adversary. In this case, the adversary may have access to the (locked) GDSII (at an offshore foundry) and the activated chip. In both cases, the adversary can retrieve the *locked gate-level netlist* from either locked GDSII or activated chip by reverse engineering [8].

### 2) ACCESS TO THE ORACLE

The adversary has access to an activated/unlocked chip. So, I/O query-based attacks like SAT are applicable to ReTrustFSM. The adversary can also utilize oracle-less attacks, such as ML-based attacks.

## 3) ACCESS TO THE TEST INFRASTRUCTURE

The adversary can access the scan chain (not stitched to the obfuscation part). Section III-D describes how this access becomes selective, and limits the adversary to a non-combinational de-obfuscation attack, like a BMC-based attack.

## 4) BASIC INFORMATION ABOUT THE OBFUSCATION TECHNIQUE

The adversary knows the obfuscation method and the location of the key gates (LFSR/counter) related to explicit external secrecy. Also, the adversary knows that part of the secrecy comes from the PIs (implicit external secrecy).

## B. EXPLICIT VS. IMPLICIT OBFUSCATION

The majority (more than 95%) [8] of logic locking techniques use the concept of **explicit external secrecy** for building their techniques. In this concept, for a circuit  $\{c_{org} : I \rightarrow O\}$ , in which  $I = \{0, 1\}^n \times \tau$  and  $O = \{0, 1\}^m \times \tau$  are the inputs/outputs sequence (sequence of *n/m*-bit inputs/outputs for  $\tau$  cycles), after obfuscating using the explicit-based secrecy augmentation, the obfuscated circuit  $\{c_{obf} : I \times K \rightarrow O\}$  requires an additional variable/input, referred to as the *key*. When the secrecy is applied to the circuit using explicit external input, it is called "key-based logic locking." In such cases, for any arbitrary obfuscated circuit  $(c_{obf})$ ,  $c_{obf}: I \times K \rightarrow O$ , where  $K = \{0, 1\}^k$  is the *key* space, there exists  $k_c \in K$  such that  $\forall i \in I \Rightarrow c_{obf}(i, k_c) = c_{org}(i)$ . On the contrary, some studies have evaluated the utilization of **implicit external secrecy** for obfuscation purposes. In this

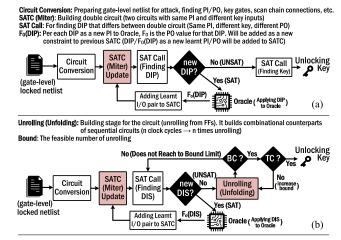

SATC: SAT Circuit (Solver's Input) DIP: Discriminating Input Pattern DIS: Discriminating Input Sequence Fo(x): Oracle Output fed by X BC: Bound Check TC: Termination Check

**FIGURE 1.** I/O query-based De-obfuscation Attacks: (a) Combinational De-obfuscation, (b) Sequential De-obfuscation.

concept, for a circuit  $\{c_{org} : I \rightarrow O\}$ , after obfuscating using the implicit-based secrecy augmentation, the obfuscated circuit  $\{c_{obf} : I \rightarrow O\}$  is still only dependent to the primary inputs, and there is no new variables/inputs, such as key input. For any arbitrary obfuscated circuit,  $\{I_1, I_2\}$  is the expected composition of input patterns, in which  $I_1$  serves as the unlocking/activation sequence, allowing the user to reach the normal mode(s) of the circuit. Since part of the input sequence is used as the unlocking condition, this model is widely used to obfuscate FSM as a keyless logic locking.

### C. I/O QUERY-BASED DE-OBFUSCATION: COMBINATIONAL VS. SEQUENTIAL

I/O query-based de-obfuscation attacks mainly focus on analyzing I/O pairs on locked/unlocked circuits to rule out the incorrect keys. Amongst them, the SAT-based techniques are most effective on a broader range of locking solutions, and they require access to the test infrastructure (scan chain) along with an unlocked/activated circuit (oracle) to target each combinational logic (CL) that is accessible directly via the scan chain, known as combinational de-obfuscation [9]. In a combinational SAT-based attack, as shown in Fig. 1(a), for each obfuscated combinational logic CL<sub>i</sub> ("locked netlist"), the attacker converts the netlist to be understandable by parsers (defining key gates, adding key inputs, etc.). Then, a (distinguishing) miter (SAT) circuit (SATC) is built as miter  $\equiv CL_{i-copv1}(dip, k_1) \neq CL_{i-copv2}(dip, k_2)$ . The SAT call on this circuit returns a distinguishing input pattern (dip) that produces different output(s) for two different keys,  $k_1$  and  $k_2$ . Later, through the scan chain, the *dip* is evaluated on  $CL_i$ of the unlocked chip (*oracle*,  $F_0$ ), and the outcome is added as a constraint  $CL_{i-copy1}(dip, k_1) = CL_{i-copy2}(dip, k_2) =$  $F_O(dip)$  for the next iterations, and this continues until there is no new *dip* (UNSAT). Finally, with one more SAT call on all *dips*, there exists one key that satisfies the condition, which is the correct key.

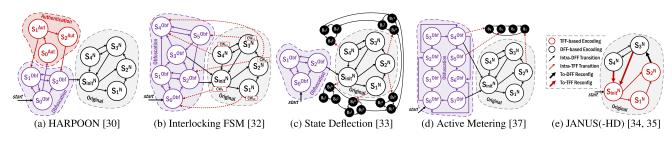

FIGURE 2. Existing FSM obfuscation solutions.

The combinational SAT-based de-obfuscation is not applicable if there is no/partial access to the scan chain. As in this case, an adversary can only rely on primary input and output (PI/PO) for an I/O query-based (like SAT-based) deobfuscation attack, the circuit state needs to be taken into account during the de-obfuscation. To do so, FFs will be cut off, and FFs' I/O becomes new circuit PO/PIs. So, in the *miter*, the attacker can apply the initial state directly to the FFs and read them out after capturing. In this case, unrolling (unfolding) cascades the design with one more copy to resemble clock cycle sequences. So, with SAT call, the attacker finds the distinguishing input sequences (DIS) for the whole design (dis with length equals with the number of unrolling). After finding all dises with the current length, unrolling (unfolding) happens for finding dises with the new length. This continues until the attack reaches the threshold bound (BC) or the following termination conditions (TC):

(i) unique completion (UC):

$\forall dis \; \exists !k_c \; [CU_{copy_i}(dis, k_c) = F_O(dis)]$

(ii) combinational equivalence (CE):

$\forall dis \; \exists k_{1,2} \; [CU_{copv_1}(dis, k_1) = CU_{copv_2}(dis, k_2)]$

(iii) unbounded model check (UMC):

$\nexists dis, k_{1,2} \mid_{\tau=\infty} [CU_{copy_1}(dis, k_1) \neq CU_{copy_2}(dis, k_2)]$

Due to the duplication and unrolling factors in both attacks (see Fig. 1), the de-obfuscation is not scalable (particularly, the sequential one (Fig. 1(b)) [42]. Thus, limiting scan chain access is an effective approach to combat existing threats that make the problem more complex [43]. Also, the explicit declaration of external secrecy is crucial to successfully setting up and applying a de-obfuscation attack. This is the main incentive for FSM-based obfuscation techniques that mostly rely on keyless (implicit secrecy) obfuscation.

#### D. FSM OBFUSCATION: PRIOR ART

Prior FSM obfuscation schemes mostly manipulate the STG of the circuits' controller(s) using implicit external secrecy [28], [30], [31], [32], [33], [34], [35], [37], [38], [39]. The augmentation of the original STG can be done by expanding (i) the state space, (ii) the transition space, or (iii) a combination of both. Fig. 2 shows how these methods

work.<sup>1</sup> HARPOON, depicted in Fig. 2(a), augments the targeted FSM by adding obfuscation and authentication modes, whose traversal is required before reaching out to the original states [30]. So, for the circuit obfuscated by HARPOON,  $c_{obf}: I \rightarrow O$ , the expected composition of input patterns must be like  $I = \{I_{en}, I_{auth}, I_{norm}\}$ , where  $I_{en}$  denotes the unlocking sequence  $(S_0^{Obf} \rightarrow S_2^{Obf})$  for obfuscation mode,  $I_{auth}$  is the authentication sequence  $(S_0^{Aut} \rightarrow S_2^{Aut})$  for authentication mode, and Inorm is the normal stimulus on the original FSM  $(S_{init}^N, S_1^N, \ldots, S_4^N)$ . Similarly, approaches like *interlocking*, dynamic state deflection, and active metering augment the FSM by inserting new modes [31], [32], [33], [37], [38]. For instance, *interlocking*, shown in Fig. 2(b), augments the original FSM by adding the same preceding obfuscation states  $(S_0^{Obf}, \ldots, S_5^{Obf})$  like HARPOON. However, they extend the FSM encoding as well as transition function by adding a code-word  $(CW_i)$  in a way each {transition, code-word} is dependent on the previous {state, code-word}, and there exists an initial code-word requirement  $(CW_0 \rightarrow S_{init}^N)$  that can be considered as the explicit external secrecy [32].

Some other studies use explicit external secrecy (keybased) for FSM obfuscation [28], [34], [35], [39], such as the usage of routing-based obfuscation or key-based counter enumeration for FSM retouching [28], [39]. Li et al. proposed JANUS(-HD), in which the encoding depends on the configuration of the state FFs. As shown in Fig. 2(e), The STG is split into two parts (red and black) whose transition and encoding are based on a specific FF type (D-FF or T-FF). Since it is built based on the different behavior in D-FF (data) and T-FF (toggle), crossing from one mode to another mode (red/T-FF  $\leftrightarrow$  black/D-FF) needs an encoding update. So, based on the current state and input patterns, the configuration needs to be updated, and it is done by a configurable MUX (switching between modes). Since the configuration of the FFs stored in a tamper-proof-memory (input to the FSM circuitry), it acts as explicit secrecy.

#### E. EXISTING ATTACKS ON FSM LOCKING

I/O query-based de-obfuscation attacks, i.e., the SAT/BMC, are formulated in a way that makes them only applicable to key-based obfuscation techniques. However, different studies evaluated a {structural+functional} attack on obfuscated

<sup>1</sup>For few cases, such as *code-word* of interlocking FSM [32] or FF configuration in JANUS [34], [35], the external secrecy is defined explicitly.

FSMs [31], [38]. This attack relies on the fact that the obfuscation part is decoupled from the original part (Fig. 2(a-d)). So, if the adversary, which has access to the netlist, can detect the FFs of FSM circuitry and then tries to re-construct the STG, then the original part can be readily distinguished through the following steps:

#### 1) TOPOLOGICAL/STRUCTURAL ANALYSIS

This step is for distinguishing and decoupling FSM FFs from other FFs (like datapath FFs). The topological analysis consists of steps like (i) identifying FFs whose input contains a combinational feedback path from their output (combinational logic for building next state logic), (2) grouping the FFs controlled by the same set of signals, and (3) finding strongly connected components (SCC) using Tarjan's algorithm [44], [45].

#### 2) FUNCTIONAL ANALYSIS

After extracting a pool of potential FSM FFs, the STG is built through functional analysis. This is done by first attempting to find the initial state, and then identifying the reachable states by creating a reduced binary decision diagram (BDD) or using a SAT solver.

#### MATCHING/EXTRACTING ORIGINAL FSM

After extracting the STG, the original part of FSM is retrieved based on some behavioral specifications. In most FSM obfuscation solutions, as demonstrated in Fig. II-D, distinguishing between the original part and the other modes is not very challenging, as these parts are not strongly connected components. In this step, for complex cases that are hard to distinguish between original and extra states, some random stimuli can be matched with the oracle.

More recent studies on FSM obfuscation show how even implicit external secrecy (keyless) can be modeled using I/O query-based attacks [29], [41]. In RANE [41], the secret(s) of HARPOON, which are  $S_{init}^N$ ,  $I_{en}$ , and  $I_{auth}$  (Fig. 2(a)), are modeled as explicit secrecy and followed by the BMC invocation for finding the secrets that show more scalability versus the {structural+functional} attack. The attack consists of two main parts: (1) finding the initial state, and (2) finding the *unlocking+authentication* sequence. In Fun-SAT [29], the minimum number of unrolling needed to find the unlocking/authentication sequence ( $I_{en}$  and  $I_{auth}$ ) is determined based on bounded-depth function corruptibility (FC) analysis that allow the attack to directly jump to the depth leading to the final satisfying assignment(s).

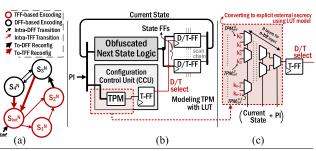

Similar methodology can even be deployed on newer FSM obfuscation techniques, e.g., JANUS or JANUS-HD [34], [35] (Fig. 3(a)), which tries to thwart the usage of any I/O query-based attacks. In this case, as shown in Fig. 3(a,b), the configuration of FFs (D/T select), as the secret, is stored in a tamper-proof-memory (TPM), and depending on the current state and the input patterns, this configuration can be updated (based on the value of corresponding  $TPM_{cell}$ ).

D/T-FF: Configurable DFF or TFF; TPM: Tamper-proof Memory; TPM<sub>cell</sub>: I<sup>th</sup> Cell of Tamper-proof memory; D/T select: Config. value for D/T-FFs; PI: Primary Input Sequence; ki: key input i designed as the I<sup>th</sup> TPM cell

**FIGURE 3.** I/O query-based attack on FSM obfuscation: (a) JANUS(-HD) [34], [35], (b) JANUS(-HD) architecture [34], [35], (c) Converting memory cell contents (*TPM*<sup>i</sup><sub>cell</sub>) to external explicit secrecy (*k*<sub>i</sub>) using LUT (To build BMC attack model).

However, as shown in Fig. 3(b,c), one can formulate the whole configuration unit (CCU) module as a small fully configurable logic (e.g., look-up-table (LUT)), in which the current state + PI defines which configuration should be selected, and each configuration bit ( $k_i$ ) serves as one  $TPM_{cell}$  ( $TPM_{cell}^i$ ). So, considering the configuration of the LUT as the secret, it becomes an obfuscation with explicit external secrecy. Hence, the security of such a technique can be undermined by the invocation of SAT/BMC.<sup>2</sup>

#### III. PROPOSED SCHEME: ReTrustFSM

To build a robust FSM obfuscation against the attacks, a set of crucial requirements must be met, which are as follows:

$REQ_1$  Hybrid Approach With High Correlation Between Explicit and Implicit Secrecy: Existing attacks show how I/O query-based attacks can challenge implicit-based FSM augmentation. Also, they do not meet the SCC requirement. However, FSM complexity can be increased by implicit secrecy. On the other side, explicit-based ones follow SCC, but none of the existing ones are robust I/O query-based attacks as they cannot expand the search space enough. To have the best of both worlds, these two can be combined for FSM obfuscation by (i) obfuscating the internal FSM transition function via explicit secrecy and (ii) expanding the search space by implicit secrecy.

*REQ*<sub>2</sub> No Structural/Functional Traceable Information: The obfuscated design must provide the adversary with the least amount of information (indistinguishability needed for logic locking [8]). The original STG of all except JANUS's in Fig. 2 can be recovered after {structural+functional} analysis as the added states is not part of the SCC of the original FSM. Therefore, FSM obfuscation must be in a way that (1) it is challenging to distinguish FSM FFs, and (2) re-constructing STG becomes difficult or leads to an incorrect one.

$REQ_3$  Applicable to All FSMs: In techniques like JANUS(-HD), the targets of obfuscation must be a point that allows the designers to split the STG into two parts while the

<sup>&</sup>lt;sup>2</sup>As this work assumed scan chain open, SAT can be applied directly to CCU. Since CCU is small (for a few transitions), the LUT counterpart will be small enough which makes the de-obfuscation time significantly shorter.

number of cutting edges is minimal to reduce the required size for the TPM that is part of CCU, as demonstrated in Fig. 3. Meeting such requirements always limits the applicability of a method. Therefore, any arbitrary FSM should be obfuscated with no challenge.

*REQ*<sub>4</sub> *Boosting Robustness by Manipulating Original Behavior of FSM:* FSM determines how the datapath is controlled, so manipulating its behavior can make de-obfuscation more complex while not affecting functionality. For example, the output of a circuit with valid/ready signals can be masked to 0 (no switching activity) when there is no valid data. Understanding such signals also helps the adversary narrow the modeling (skipping unrollings). It is possible to prevent such reduction by increasing the frequency of output updates (either valid is 1 or 0), based on the power budget, and enhancing the search space for pruning by using the handshaking/communication signals.

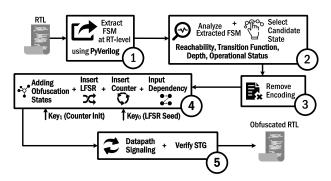

#### A. OVERVIEW OF ReTrustFSM

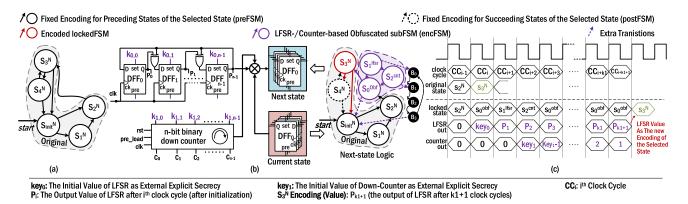

ReTrustFSM proposes multiple components that apply obfuscation at RTL to meet  $REQs_{1-4}$ . Fig. 4 shows how ReTrustFSM retouches the FSM of the circuit for obfuscation purposes. In ReTrustFSM, the original (black part) and obfuscated (purple part) FSMs are systematically twisted together (tightly coupled for building SCC in which the obfuscated FSM is in the middle of the original FSM). By doing so, it becomes difficult (almost impossible) for the adversary to distinguish between original and obfuscated states (no target for the initial state to separate these two parts). So, approaches like fun-SAT [29] and RANE [41] are not applicable as there is no initial state as the main target.

ReTrustFSM also utilizes both key-based (explicit) counter-based and LFSR-based obfuscation for STG traversals and implicit secrecy for the traversal of the obfuscated FSM. So, to have a correct connection between two splits of the original FSM (through obfuscated FSM), both explicit and implicit secrecy must be correct. Without correct traversal of the obfuscated FSM, the FSM is pushed towards the initial state, meaning that the expected (correct) functionality is not acquired (malfunctioned). Moreover, the expected behavior of the obfuscated FSM depends on both implicit and explicit external secrecy. Considering the example depicted in Fig. 4, the following shows the key components of ReTrustFSM and how they work:

#### 1) MIXING OBFUSCATED STATES WITH ORIGINAL STATES

As shown previously in Fig. 2(a-d), in existing FSM obfuscation methods, the obfuscation states are separated from the original states and they do not create an SCC together [31], making them vulnerable to {structural+functional} attack. So, to deter such an attack, obfuscation states must be wellblended with the original FSM states in such a way that the Tarjan's algorithm [45], or any similar one, cannot distinguish the obfuscation states from the original states. Hence, in ReTrustFSM, the obfuscated region  $(S_0^{Obf}, S_1^{lfsr}, S_2^{cnt})$  and

their related transitions in Fig. 4), called encFSM, is completely mixed and twisted as an intermediate sub-FSM into the original FSM. Based on the specification of encFSM, it may split the original FSM into three sub-FSMs, as we call them preFSM, lockedFSM, and postFSM. preFSM is the first fixed part of the original FSM as the preceding states of the **encFSM**  $(S_{init}^N, S_1^N, S_2^N)$  and their edges in Fig. 4). postFSM is another fixed (could be dynamic as well) part of the original FSM as the succeeding states of the encFSM  $(S_4^N \text{ and their edges in Fig. 4})$ . **lockedFSM** is the connecting state (and its outgoing transitions) between the encFSM and **postFSM** ( $S_3^N$  and their edges in Fig. 4). Additionally, all transitions between encFSM and preFSM, lockedFSM, and postFSM are populated (once the correctness of secrecies is not met) to build a unified SCC. Details of these terminologies and their roles in ReTrustFSM are discussed shortly in Section III-B.

#### 2) MIXING KEYLESS AND KEY-BASED FSM OBFUSCATION

Since the key-based obfuscation techniques are vulnerable to SAT/BMC attacks, and keyless obfuscation methods are vulnerable to {structural+functional} attack [31], we introduce a sophisticated hybrid approach in ReTrustFSM combining both key-based (explicit external secrecy) and keyless obfuscation (implicit external secrecy). To do that, traversal of encFSM, that allows correctly connecting preFSM to lockedFSM and then to postFSM, ReTrustFSM requires both explicit external secrecy (key input) as the configuration of counter and LFSR and implicit external secrecy (primary input) as the internal transitions of the encFSM. With these two secrets, the connection between (preFSM, lockedFSM, and postFSM) will be established correctly  $(S_2^N \rightarrow S_3^N)$ , thereby the original FSM will be reconstructed. As keyless and key-based obfuscation approaches are orthogonal, they individually combat the SAT/BMC and {structural+functional} attacks, respectively.

#### 3) OBFUSCATION-ORIENTED STATES ENCODING

In ReTrustFSM, the encoding of **lockedFSM** (red parts including  $S_3^N$  and its outgoing transitions) is calculated by the **encFSM** at run-time. So, it becomes dependent on the execution of the obfuscated counter and LFSR that is located within **encFSM**. Without correct traversal of the **encFSM**, the succeeding states do not work correctly, leading to invalid signaling to the datapath (malfunctioning). The inclusion of state encoding makes ReTrustFSM resistant to removal attacks.

#### B. STATE ENCODE BY EXPLICIT EXTERNAL SECRECY

In ReTrustFSM, we associate lockedFSM and its outgoing transition function with internal computations of the encFSM. Fig. 4 shows how ReTrustFSM builds this concept by integrating key-based LFSR and counters. As shown, in encFSM, the key input as the explicit secrecy ( $key_{0/1}$ ) determines how the LFSR/counter will operate in the encFSM, and based on their values, the encoding of lockedFSM will be calculated.

FIGURE 4. Proposed ReTrustFSM: (a) original FSM, (b) obfuscated FSM, (c) Activation: From LFSR/counter initialization to encoding.

FIGURE 5. The proposed FSM obfuscation flow.

**FIGURE 6.** Selection of candidate in ReTrustFSM to avoid bypassing of encFSM.

Fig. 4(a,b) show the original vs. obfuscated FSM after applying the proposed scheme, respectively, and Fig. 4(c) shows a timing diagram of how activation works for correctly encoding encFSM ( $S_3^N$ ). From preFSM to encFSM ( $S_N^2 \rightarrow S_0^{cnt}$ ), the LFSR is initiated with part of explicit external secrecy (*key*<sub>0</sub>). Similarly, during encFSM ( $S_1^{lfsr} \rightarrow S_2^{cnt}$ ), the down counter is initiated with another part of explicit external secrecy (*key*<sub>1</sub>). Then, once the down counter reaches 1, the current value of LFSR will be used as the encoding of the lockedFSM state ( $S_N^3$ ).

Fig. 5 shows the main steps of ReTrustFSM obfuscation flow whose details are discussed below.

#### 1) FSM EXTRACTION AT RTL

ReTrustFSM framework is equipped with *PyVerilog* [46], allowing us to extract all the crucial information of the

original FSM, e.g., states space/encoding, initial state, and state transition function.

#### 2) CANDIDATE STATE ANALYSIS + SELECTION

In ReTrustFSM, candidate states should possess the following properties:

Lemma 1: A candidate is the immediate next state after encFSM and must be the only connection between preFSM and postFSM. It means postFSM must have NO direct in-degree transition from the preFSM. This property ensures that the obfuscation states (encFSM) cannot be bypassed.

In ReTrustFSM, the candidate state is the immediate next state after encFSM. Since both preFSM and postFSM are implemented using fixed encoding, if there exists more than one path from preFSM to postFSM, the encFSM and lockedFSM might be bypassed while some part of the functionality is still available in postFSM (e.g., moving from decoding to execution in a processor). Following Lemma 1 enforces every run to first traverse encFSM (before lockedFSM and postFSM). Also, since the candidate must have only one in-degree transition from the preFSM, meeting this property guarantees that the candidate state is one of the intermediate states (the initial state will no longer be a candidate). Fig. 6 illustrates different scenarios and how bypassing might happen if the candidate does not possess Lemma 1. In Fig. 6(a), as ReTrustFSM selects  $S_{1nit}^N$  as the candidate, after the insertion of the encFSM on  $S_{init}^N \rightarrow S_1^N$ , there exists more than one (two) in-degree transitions from preFSM to postFSM (i.e.,  $S_1^N \rightarrow S_2^N$  and  $S_{init}^N \rightarrow S_2^N$ ). So, the encFSM can be bypassed through the other transition which has no obfuscated state and the adversary might still achieve the functionality by bypassing state  $S_1^N$ . Fig. 6(b-d), shows three other scenarios where candidates  $(S_2^N \text{ or } S_3^N)$  follows Lemma 1 and bypassing is no longer possible.

Meeting such property might look like a strict condition that limits the choices of the candidate state for the proposed framework. However, analysis of the benchmark circuits and real applications shows that a significant portion of FSM states in all circuits meet this criterion, and this is mostly because of the sequential nature of the controller's behavior. *Lemma 1* can be extended in ReTrustFSM from one state selection to multiple states selection. In this case, any state member of postFSM can be part of lockedFSM. For instance, based on Fig. 4, the encoding of both  $S_3^N$  and  $S_4^N$  can be determined by the LFSR/counter. In this case, for I/O query-based attacks, more iterations would be required for re-constructing both states' encoding vs. the case only the immediate state after encFSM is chosen.

Lemma 2: The lockedFSM with encoding should involve such states that feed the datapath circuitry. This property ensures that obfuscating the FSM using ReTrustFSM surely corrupts the datapath circuitry (like the flow of data) so that the design is dysfunctional without the correct secrets.

Based on how the FSM is operating, the controlling signals are defined and sent to the datapath side, which determines the functionality and behavior of the design. Hence, from both functionality as well as corruptibility points of view, the candidate selection would be a crucial step in the proposed framework. As an example in Fig. 4(a), assuming that  $S_3^N$  performs the execution step and configures necessary datapaths' registers, it would be a better candidate as it can affect a higher portion of computations within the datapath.

Lemma 3: The lockedFSM with encoding should involve such states that are located at the deepest stage of the FSM.

From the adversary's point of view, assuming that the adversary will apply the I/O query-based attack, e.g., SAT/BMC, targeting and obfuscating the latest stages of the FSM would be a booster as it requires deeper calculation, such as more unrolling for the combinational counterpart creation and larger bound checking. For instance, To observe the output of the circuit after arriving at  $S_3^N$ , the adversary requires at least 4 times unrolling (resembling 4 clock cycles). However, for states like  $S_2^N$ , it would be in the range of 1-2 cycles for the first observation. We experimentally validated the significance of these Lemmas 1, 2, and 3 in Table 3 by performing BMC attack on the ReTrustFSM obfuscated design of Fig. 6 for varying candidate states.

#### 3) REMOVAL OF STATE ENCODING

Once the candidate states are selected, then their original state encoding is removed from the design RTL. We assume that the designer has manually defined the encoding using some constant/parameter definition with desired encoding format (binary, one-hot, gray, etc.). The encoding of these states is later driven by the LFSR state which is discussed below.

## 4) INSERTION OF OBFUSCATION STATES AND ALL RELATED COMPONENTS

This step adds the obfuscated states (encFSM) based on the selected candidate(s). In Fig. 4,  $S_3^N$  has been selected as the candidate, thereby ReTrustFSM will insert the encFSM on transition  $S_2^N \rightarrow S_3^N$ . The states of encFSM (the purple states) are the following three additional states:

## a: $S_0^{obf}$

This state determines whether the traversal of the encFSM is required or not. In ReTrustFSM, to avoid performance/throughput degradation, the traversal of the encFSM will be accomplished only once after power-on (activation). So, if the encFSM is already traversed once, the encoding of the candidate state  $(S_3^N)$  has already been done by the LFSR, and the state machine can go directly to the candidate state. We implemented a one-bit flag check to see whether the traversal of the encFSM is needed or not. At power-on, the flag is set to zero. Once the flag is zero, the encFSM must be passed first to configure the lockedFSM register(s). Through the  $S_2^{cnt} \rightarrow S_0^{obf}$  traversal, the flag will be set to 1. Additionally, in this state, as also shown in Fig 4(c), ReTrustFSM initializes the LFSR circuitry by using the explicit external secrecy  $key_0$ . For an incorrect value of the external secrecy, the next states lead to an incorrect encoding for the candidate state, which results in returning back to  $S_{init}^N$  (becomes dysfunctional).

## b: $S_1^{lfsr}$

In this state, as shown in Fig 4(c), ReTrustFSM starts updating the LFSR based on its initialized value (starting of the shift). In ReTrustFSM, to ensure that the obfuscation circuitry, e.g., LFSR, and down-counter, is strongly connected with the original FSM, the initialization of the LFSR is controlled by the next state circuitry while the provided key is incorrect. This allows us to fully twist the logic dedicated to the original FSM with that of the encFSM. This significantly helps to immobilize step 1 of {structural+functional} attack [31], [45], which is Tarjan-based topological analysis. To implement this, we do not need to insert a MUX-based encoding selection between correct/incorrect state value(s) for the correct/incorrect key. Since the design team is aware of the location of encFSM in the STG, the encoding of the preceding state (the latest state of preFSM) is known. For instance, as demonstrated in Fig. 4,  $S_2^N$  is the immediate state before encFSM with a known (fixed) encoding value. So, to build this twist, we just need to add XOR operation for the key value and the preceding state encoding, whose output produces the correct encoding. For instance, in Fig. 4, the value of  $key_0$  can be defined in a way that  $key_0 \oplus S_2^{\bar{N}}$  results in producing the correct initial for the LFSR that led to the correct  $S_3^N$  encoding (after down counting). So, in this case, the XOR-based model does not reveal any combination of incorrect/correct keys to the attacker. Once initialized, the LFSR starts shifting/shuffling per each clock cycle, and the encFSM goes to the  $S_2^{cnt}$  state.

## c: $S_2^{cnt}$

This state initializes the down-counter with the other part of explicit external secrecy ( $key_1$ ) as the initial count value, and the counter starts down-counting until it reaches 1, as shown in Fig. 4(c). The counter drives the LFSR to encode the

candidate state  $(S_3^N)$  after  $key_1$  clock cycles during run time.  $S_2^{cnt}$  state then goes to the  $S_0^{obf}$  state. If the LFSR and the down-counter are initialized cor-

If the LFSR and the down-counter are initialized correctly (correct  $key_{0/1}$ ), the down-counter counts correctly, allowing the LFSR to be in a current value for encoding the candidate state  $S_3^N$ . In the event of an incorrect external secret (incorrect  $key_{0/1}$ ), the candidate state  $S_3^N$  is encoded with an incorrect value. Hence, they are discarded from the original state machine and the obfuscation states move the state machine to some incorrect states (e.g., black holes  $B_{0:3}$  or initial state  $S_{init}^N$  in Fig. 4(b)). It is also noteworthy that, once the obfuscated FSM is unlocked, only  $S_0^{obf}$  state stays in the state machine during regular operation, thereby no throughput degradation will be experienced after unlocking. Additionally, ReTrustFSM can produce false responses at PO once the state machine is in state  $S_0^{obf}$  with no valid signal. This increases the frequency of output updates that enhance the robustness against I/O query-based attacks ( $REQ_4$ ).

#### 5) FUNCTIONAL VERIFICATION WITH INCLUSION OF DATAPATH

Once the insertion of obfuscation states, LFSR, downcounter, and all extra populating transitions is done, ReTrustFSM will verify the functionality between the original and obfuscated circuit while the secrets are provided. In this case, the inclusion of the datapath is crucial as the signaling between the controller and datapath needs to be functionality verified while the encoding is updated and new intermediate states are added. Researchers have investigated how don't care states in FSM can be exploited to insert hardware Trojans and faults [47]. Therefore, ReTrustFSM inserts default case to define any don't care states in the design and eliminate any existing FSM vulnerabilities [48].

#### C. STATE EXPANSION USING IMPLICIT SECRECY

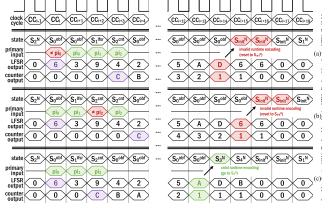

To boost the robustness of ReTrustFSM, particularly against I/O query-based attacks, we deploy a hybrid approach for FSM obfuscation, by establishing a deep correlation between the key-based (explicit external) encoding and key-less (implicit external) obfuscation. To accomplish this, the state transitions within encFSM ( $S_0^{obf} \rightarrow S_1^{lfsr} \rightarrow S_2^{cnt}$  in Fig. 4) have been associated to the input patterns at specific clock cycles. So, for clock cycles  $cc_{i,i+1,i+2}$ , shown in Fig. 4(c), specific patterns must be observed at PI allowing encFSM to be traversed cycle accurately as expected.

Fig. 7 demonstrates how this implicit secrecy works in ReTrustFSM for a 4-bit FSM, while a 4-bit LFSR and counter are integrated. It shows that since the LFSR/counter initialization happens at different clock cycles, incorrect traversal of encFSM states results in having incorrect LFSR value for encoding while the down-counter reaches 1. So, the candidate state will be discarded from the FSM, making the circuit dysfunctional (Fig. 7(a,b)). The implicit secrecy that is dependent on patterns driven by the PI creates functional obscurity and protects the encFSM with the explicit secrecy for the

**FIGURE 7.** Implicit external secrecy for the example of Fig. 4. Correct  $\{k_0, k_1\} = \{0110, 1100\}$ , and LFSR equation is  $x^3 + 1$ . Incorrect input pattern (cycle inaccurate) for (a)  $S_0^{obf} \rightarrow S_1^{lfsr}$ , (b)  $S_0^{lfsr} \rightarrow S_1^{ont}$ , and (c)  $S_0^{ont} \rightarrow S_1^{obf}$ .

state encoding. Using such a structure, the keyless and the key-based components of ReTrustFSM are correlated to each other during the unlocking and functional phase, to aid in the cycle-accurate functioning of the design.

It is evident that since the implicit external secrecy must be applied at specific clock cycles (in the middle of the first round of execution), the activation may look challenging. However, similar to other sequential FSM-based obfuscation techniques, the whole sequence of input patterns for one full FSM round with the inclusion of encFSM traversal will be the implicit external secrecy. For instance, for Fig. 4, any input pattern sequence allowing us to reach  $S_2^N$ , followed by the specific implicit external secrecy needed to pass encFSM, plus any input pattern sequence allowing us to reach  $S_{init}^N$ will be considered as a sequence for implicit external secrecy. Note that for applying a full round of input to the circuit, no additional circuitry is required, and the sequence of inputs will be applied directly (activation license).

As mentioned in Section III-B, ReTrustFSM removes the encoding of the candidate state and drives the candidate state by the LFSR state. The LFSR state defines the state transitions concerning the candidate state. However, the candidate state is defined by some constant/parameter which is a secret in this case. Having any secret value hard-coded in the RTL could make the design vulnerable to functional analysis-based structural attack [13]. To eliminate any structural trace from the design, stealthy opaque predicate [49] based dynamic secrecy generation can be deployed. To know more about how opaque predicate can be utilized for generating obfuscated constants in the RTL, we direct the readers to [49].

As mentioned previously, the traversal related to the LFSR and the down-counter (counting and shifting) will continue till the down-counter reaches one. This means that for the down-counter with greater initial values (greater exact value of external secrecy), it takes more time to calculate the encoding value of the candidate state. This shows one of the unique features of ReTrustFSM, where it makes a relation between the exact value of the explicit external secrecy and the robustness of the approach. However, it may result in building a backdoor for attacking this mechanism. For instance, for correct case demonstrated in Fig. 7(c), the explicit secrecy pair for the LFSR and the down-counter  $(\{k_{0,0:3}, k_{1,0:3}\})$  is set to {0110, 1100}, and for the correct traversal, the down-counter must be initialized two clock cycles after the LFSR (LFSR at  $cc_i$  and down-counter at  $cc_{i+2}$ ). So, for any pair of the LFSR and the down-counter values demonstrated in Fig. 7(c) with two clock cycles difference, it can be considered as the correct value of the external secrecy. For instance, {0011, 1011}, which is the LFSR value at  $cc_{i+1}$  and down-counter at  $cc_{i+3}$ , could be another correct value of the external secrecy, that also needs one less clock cycle execution to reach down-counter to one. Having such knowledge allows the adversary to fix the downcounter to a small value, and run the I/O query-based BMC for the other part of the secrecy that is related to LFSR, and since it requires few traversals, the BMC will break it very fast.<sup>3</sup> So, for two purposes, which are (1) avoiding having multiple correct key pairs, and (2) avoiding the possibility of running fix and run partial BMC, we re-use one of the external secrecies with targeted value to obfuscate part of the design, e.g., the next state logic. It constrains the key value to the expected (targeted) one. Using such constraining limits the correct key to only 0110+1100, and enforces the attacker to run the BMC to the depth as expected, and additionally, it reduces the number of possible correct keys to only one. All the experimental results demonstrated in Section V are captured after applying this constraint. Please note that adding constraint for one part of the external secrecy would be enough to completely mitigate this issue.

#### D. NECESSITY OF SCAN PROTECTION

Manufacturing testability provides access to internal circuit states to achieve high test coverage. Debug engineers (from the foundry or test facility) can inspect the concurrent state of the sequential elements in case of manufacturing errors. Capitalizing privilege access to internal state registers does not reveal any secret meta-data in existing FSM obfuscation techniques that use implicit secrecy since no explicit representation of secrecy exists, and the sequence of input patterns serves as unlocking/authenticating sequences. The adversary needs to check all possible transactions to reconstruct the obfuscated FSM if the state registers are known. As a result, while only implicit secrecy is maintained, the test infrastructure may not provide any clues to an adversary. Assume there is explicit secrecy in place. In that case, it may reveal secret meta-data (e.g., the current state of the FSM, the state registers' output/input) concerning the underlying obfuscation method, as the propagation of intermediate variables might reveal something about the explicit secrecy (information leakage). Therefore, for existing FSM obfuscation methods, they may rely on various scan chain securing methods [38]. As discussed in Section II-E, JANUS(-HD) [34], [35] performs FSM obfuscation by deploying reconfigurable D-T flip-flops where a control signal (stored in TPM) decides the role of the flip-flop (either D-type or T-type). The role of the individual reconfigurable state registers (D-type or T-type) is the main secret in the case of JANUS(-HD), and it is assumed that the attacker has full access to the chain. However, having such privileged access to the scan chain, the attacker can initiate a scan-based attack [50] to reveal this explicit secrecy that determines the state register type (D-type or T-type) of the reconfigurable FFs in JANUS(-HD). This can be done by flushing the scan chain with a known pattern and inspecting the location of bit flips in the scan-out response.

Since ReTrustFSM uses both key-based and keyless obfuscation, some registers dedicated to obfuscation may be targeted as sources of information leakage. In ReTrustFSM, security information is contained in register resources dedicated to state encoding, LFSR, and counters. To deter these scan-based attacks, ReTrustFSM assumes the design is fullscan capable and protected by state-of-the-art scan obfuscation techniques [51] to shield these register contents. To keep the scan chain as open as possible, we only obfuscate the chains that include the targeted registers. Despite being a closed scan chain, the DFT structure still makes different chains fully accessible. Our experiments demonstrate that this approach allows for a high test coverage when multiple scan chains are inserted. It also provides a higher level of observability/controllability to the designer while not compromising security for the obfuscated secrets.

#### IV. DETAILED SECURITY ANALYSIS OF ReTrustFSM

This section provides a detailed security analysis of ReTrustFSM. Considering the I/O query-based BMC attack as an algorithmic approach applicable to FSM obfuscation, and based on the combinatorial complexity of the constraint satisfaction problem, we define the security metric of ReTrustFSM and predicts the security complexity in terms of BMC attacks using a machine-learning (ML) model by extracting a set of features. Furthermore, we evaluate ReTrustFSM against a {structural+functional} attack [31], removal-based attack, functionally guided SAT attack [29], and an Oracle-less machine-learning-based attack [52].

#### A. OPERATIONAL MODEL AND BMC COMPLEXITY

The SAT and BMC attacks are algorithmic attacks defined on logic locking [9], [41]. In ReTrustFSM, since part of the secrecy is the implicit external secrecy provided by the primary inputs, even though the scan chain is fully accessible, the possibility of running SAT attack (modeling primary inputs as secret) is almost zero. Hence, this section evaluates the possibility of a BMC attack where the adversary needs (1) PI/PO access to the activated chip (oracle, and (2) PI/PI

$<sup>^{3}\</sup>mathrm{The}$  same can happen by fixing the LFSR and running the BMC on the secret of the counter.

access to the gate-level netlist. The BMC helps find the best set of I/O pairs, leading to the secrets.

As discussed in Sec. III, the key-based state encoding of ReTrustFSM is driven by an LFSR/counter configuration. Assuming that the LFSR is  $k_0$  bits wide, the *characteristic polynomial* of a  $k_0$ -bit LFSR with  $c_0, c_1, \ldots, c_{k_0-1}$  feedback coefficient can be represented by the following Equ. 1.

$$P(l) = 1 + c_0 l_0^t + c_1 l_1^t + \dots + c_{k_0 - 1} l_{k_0 - 1}^t$$

(1)

Eqn. 1 is a univariate monic polynomial that can be represented by a Frobenius companion matrix [51]. Equ. 2 and Equ. 3 show the companion matrix that can represent the succeeding states of the LFSR (based on the coefficients and its initial value) and its simplified form, respectively.

$$\begin{bmatrix} l_0 \\ l_1 \\ l_2 \\ \vdots \\ l_{k_0-1} \end{bmatrix}^{t+1} = \begin{bmatrix} c_0 & c_1 & c_2 & \vdots & \vdots & c_{k_0-1} \\ 1 & 0 & 0 & \vdots & \vdots & 0 \\ 0 & 1 & 0 & \vdots & \vdots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & 0 & 1 & 0 \end{bmatrix} \cdot \begin{bmatrix} l_0 \\ l_1 \\ l_2 \\ \vdots \\ l_{k_0-1} \end{bmatrix}^t$$

$$L^{t+1} = A \cdot L^t$$

(3)

In ReTrustFSM, once the obfuscated circuit is powered on, the explicit secrecies, i.e. initial secret seed and initial counter value, is loaded into the LFSR and the down-counter, respectively. Let us consider that the seed of the LFSR is  $L^{t}$  and the initial count value of the down-counter is  $k_1$ . As discussed previously, in ReTrustFSM, the LFSR stops traversing once the down-counter reaches one. At this moment, the current value of the LFSR is utilized to encode the obfuscated state(s), as demonstrated in Fig. 7(c) at clock cycle  $cc_{i+14}$ . So, considering that the initial states of the LFSR and downcounter constitute the secret key  $\{k_0, k_1\}$  of the circuit in ReTrustFSM, as demonstrated in Fig. 7, and assuming  $L^{t}$ as the initial seed of LFSR and  $k_1$  as the number of clock cycles to reach the current state encoding, the LFSR state that performs correct encoding of the obfuscated FSM can be represented by the Equ. 4.

$$L^{t+k_1} = A^{k_1} \cdot L^t \tag{4}$$

For BMC attack, the model checker tool must visit all succeeding states of the LFSR and down-counter, i.e., the ReTrustFSM obfuscated circuit must be unrolled for at least  $(k_1 + \delta)$  times to extract the secret seed of the LFSR, required for correct traversal. Here,  $\delta$  is related to the other sequential depth of the obfuscated FSM and the obfuscated states, e.g., the number of states that must be traversed to reach the LFSR initialization state  $(S_1^{lfsr})$ . To enable ReTrustFSM by a machine learning model that predicts the security robustness against BMC attacks, we concentrate on the features that can be extracted from the formal representation of the problems (obfuscated circuits) based on *propositional logic formula*. This security evaluation consists of three steps: (1) feature engineering, (2) training, and (3) testing and validation.

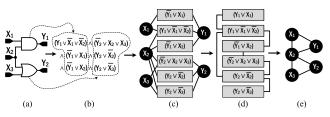

**FIGURE 8.** The CNF features predictive of the computational complexity of the SAT instance. (a) sample circuit  $CL_i$ , (b) corresponding CNF representation of  $CL_i$ , (c) VCG graph of  $CL_i$  CNF, (d) CG graph of  $CL_i$  CNF, and (e) VG graph of  $CL_i$  CNF.

*Definition 1:* A *propositional formula* is a conjunction of *clauses*. A *clause* is a disjunction of literals. A propositional variable or its negation is known as a *literal*.

#### 1) FEATURE ENGINEERING

Knowing (about the source, propagation, and usage) the explicit secrecy in ReTrustFSM  $(k_0, k_1)$  allows the designer to generate the propositional formula (in conjunctive normal form (CNF)) of the SATC (as discussed in Section II-C) based on the required/selected unrolling number.<sup>4</sup> In a SAT instance, the number of clauses, variables, and their ratio is highly correlated with the instance's empirical difficulty [53]. The authors of [54] generated a set of features that are predictive of determining the computational complexity of a SAT instance. Some of these features are derived from well-known heuristics, e.g., the number of clauses, variables, and the ratio of clauses to variables, while some others are based on more complex combinatorial properties [53]. Fig. 8 shows a visual representation of the dominant features. A sample circuit and its corresponding CNF formula is shown in Fig. 8(a) and Fig. 8(b) respectively. From Fig. 8(b), it is noticeable that the number of clauses, variables, and their ratios is 6, 5, and  $\frac{6}{5}$ , respectively. These features capture the size of the SATC generated from the ReTrustFSM obfuscated circuit (after  $\tau$ -time unrolling). The three undirected graphs in Fig. 8 correspond to three different graph representations of a SAT instance, which are defined as follows:

*Lemma 4:* A VCG graph G(V,E) is a bipartite graph of the vertex set V and edge set E, where each variable and clause  $(v_i, c_j) \in V$ . The occurrence of a variable  $v_i$  in a clause  $c_j$  represents an edge,  $(v_i \rightarrow c_j) \in E$  in the graph G.

*Lemma 5:* A CG graph G(V,E) has node for each clause,  $c_i \in V$ . Whenever two clauses share a negated literal, an edge,  $(c_i \rightarrow c_j) \in E$  is added to the graph G.

*Lemma 6:* A VG graph G(V,E) has node for each variable,  $v_i \in V$ . Whenever two variables occur together in at least one clause, an edge,  $(v_i \rightarrow v_j) \in E$  is added to G.

Fig. 8(c-e) corresponds to the VCG, CG, and VG graph representations of the CNF instance from Fig. 8(b), respectively, by following Lemma 4, 5, and 6. Each of these graphs corresponds to a constraint graph associated with the obfuscated

<sup>&</sup>lt;sup>4</sup>From SAT solver point of view, for sequential circuits, unrolling will be done as a pre-processing step to build the combinatorial counterpart.

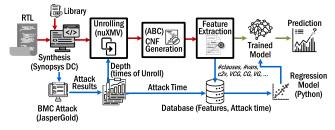

**FIGURE 9.** Linear regression based security complexity estimation model framework based on the predictive features of the ReTrustFSM obfuscated CNF instance.

circuit. Therefore, they delineate the complex combinatorial structure of the SAT instance. For a detailed understanding of all the features of a SAT instance, we direct the readers to [54]. These features can be combined with a regression-based machine learning model to construct the hardness model of the ReTrustFSM obfuscated circuit.

#### 2) MODEL TRAINING

Fig. 9 provides an overview of the ML framework that we developed for the complexity analysis of the ReTrustFSM obfuscated circuit. The blue steps in Fig. 9 are only required during the training phase while the green steps are for prediction phase. The brown steps are essential for both training and prediction. The details training phase of this ML framework is as follows:

- ml<sub>0</sub> (Synthesis): The original (unlocked) and ReTrustFSM obfuscated RTL must be synthesized in a target library using open-source [55] or commercial (Synopsys Design Compiler, or Cadence Genus) EDA tools.

- ml<sub>1</sub> (*Dataset Creation*): Once the original and obfuscated synthesized netlist is generated, we perform a BMC attack on the ReTrustFSM obfuscated circuit using the state-of-the-art BMC attack tool on sequentially obfuscated circuits [41]. If succeeded, the attack results provide the unlocking key, size of *dis* (as discussed in II-C), and time to extract the key. The time taken by the BMC attack fills the database as *target*, which the ML model later utilizes along with the feature set.

- ml<sub>2</sub> (Manual Unrolling of the De-obfuscated Circuits): The size of the dis reported by the successful BMC attacks represents the number of cycles the sequential circuit must be unrolled (or the number of copies the CU of the sequential design needs to be added in the miter SATC as discussed in Section II-C) to perform the combinational SAT attack and deduce the secret key. During the training phase, we utilize the dis number along with an in-house developed functional corruptibility-guided [29] unrolling script to generate the miter SATC of the ReTrustFSM obfuscated circuit using an open-source model-checking tool nuXMV [56].

- **ml**<sub>3</sub> (*Generation of Propositional Logic Formulas*): The  $\tau$ -time<sup>5</sup> unrolled circuit generated by the unrolling tool

<sup>5</sup>Per obfuscated circuit, different numbers of unrolling are required.

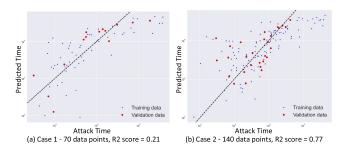

FIGURE 10. Accuracy of the linear regression-based BMC attack complexity prediction model for two different cases - (a) 70 and (b) 140 data points. Both (a) and (b) plot the predicted vs. actual BMC attack time where the blue and red dots represent the training and validation data set. The prediction accuracy metric of the linear regression model increased from (a) 0.21 to (b) 0.77 when the training size was doubled.

is in bench format. We thereby make use of the ABC synthesis tool [55] to generate the *CNF* of the unrolled version of the ReTrustFSM obfuscated circuit.

- **ml**<sub>4</sub> (*Feature Extraction of Generated CNFs*): At this step, we plug in the *CNF* representation of the ReTrustFSM obfuscated circuit to an open-source feature extraction tool [54] which generates features that are predictive of determining the computational complexity of the given SAT instance. In our analysis of ReTrustFSM, we extracted 46 features from the given CNF. These features constitute the feature set of the database.

- $\mathbf{ml}_5$  (*Regression for Training*): Once the database is ready, we deploy a linear regression algorithm to train the model based on the extracted CNF features and target BMC attack time. We utilized a *ridge regularizer* with  $\alpha = 0.022$  as error metric.

We developed a database of roughly 140 BMC attack results (details of the experimental setup and attack results are discussed in Section V) and their associated features among which 90% of the data points were used to train the linear regression model and 10% (on never-seen circuits by the model, i.e., test data set is not part of the training data set) were kept for validation.<sup>6</sup>

#### 3) TESTING AND VALIDATION

After training the ML model using the pre-generated dataset, the trained model is tested and validated on the targeted circuit(s) (To estimate the de-obfuscation time for a desired external secrecy). Fig. 10 shows the comparison between actual time and predicted time for both training (blue) and validation (red) data sets for two different training data sizes. We collected in total 140 data points and considered two cases for training, testing, and validation. In the first case, we considered half of the collected dataset (70 data points) while in the second case we considered full dataset (140 data points). For both the cases, we utilized 90% of the considered data for training (i.e., 63 data points in case one and 126 data

<sup>&</sup>lt;sup>6</sup>The size of training dataset can be increased over time, and by increasing the dataset size, higher accuracy can be achieved.

points in case two for training) the linear regression model. We validated the trained model using the residual 10% dataset of the considered data in each case (i.e., 7 data points in case one and 14 data points in case two). Accuracy of the BMC attack complexity prediction model for two different cases are presented in Fig. 10(a) and (b), respectively. The prediction accuracy metric, R2-score increased from 0.21 to 0.77 when the training data size was doubled. Hence, further expanding the training data set will increase the prediction accuracy beyond 0.77. It can also be observed from Fig. 10 that for the training data, the model mostly performed underestimation. However, the model was able to predict the validation data with an average of 90% accuracy.<sup>7</sup> It is noteworthy that the model can be trained offline with the results generated from the prior BMC attacks and its associated features. Enabling our proposed FSM obfuscation by this ML model estimator allows the designers to acquire the estimated deobfuscation time before the accomplishment of obfuscation. Based on the desired external secrecy (down-counter initial value) and the minimum number of required unrolling (which can be identified by utilizing functional corruptibility [29]), the model (unrolled version of CNF) can be generated, and the ML framework can predict the de-obfuscation time with high accuracy. Therefore, the designer can estimate security complexity of ReTrustFSM obfuscated circuit for the given external secrecy without actually performing BMC attack.

#### **B. FORMAL SECURITY EVALUATION**

The authors of [57] and [58] provided formal definitions of the security posed by logic locking. The *indistinguishable logic locking* (IND-LL) requires that the adversary cannot distinguish between a locked and an unlocked (original) circuit [57]. The *simulation secure logic locking* (SIM-LL), entails that the adversary cannot leak any additional information about the original circuit from the locked one than an oracle simulator. Later, based on these definitions, the authors of [57] and [58] formally proved that universal circuits can achieve IND-LL secure logic locking. However, for a circuit of size *n*, the universal circuit requires a key of length  $O(n \log n)$  [57] which significantly blows up the locked circuit size and suffers greatly from overhead. Therefore, to achieve IND-LL secure logic locking in practise, we contemplated two corollaries from [57] and [58].

*Corollary 1:* The IND-LL secure logic locking with smaller key size (i.e., reasonable overhead) can be achieved by the inclusion of a cryptographic assumption [57].

*Corollary 2:* Increasing the information leaked by the locked circuit can improve the locking overhead while provable security is still guaranteed [58].

*Linear feedback shift registers (LFSR)* are pseudo-random number generators vastly used for light-weight cryptographic applications. According to the Berlekamp-Massey [59],

an adversary must observe at least 2n consecutive outputs from an LFSR to reconstruct the seed (explicit external secrecy of ReTrustFSM). However, in the case of ReTrustFSM, as explained in Section III-D, circuit elements dedicated to the state encoding, LFSR, and counter are protected by the scan obfuscation method to immobilize any chance of leakage from the LFSR. Moreover, LFSR defining the state encoding can drive the preFSM to any possible state ( $2^{n-1}$  as the best case), as shown in Fig. 7. Therefore, ReTrustFSM with its explicit external secrecy can achieve IND-LL security.

#### C. STRUCTURAL AND TOPOLOGICAL ANALYSIS

The structural and topological analysis attempts to reverseengineer the FSM automatically from the obfuscated flattened gate-level netlist [31] as discussed in Section II-D. The adversary requires access to the locked gate-level netlist, and the attack is performed based on a set of structural and topological analyses. In some cases the adversary may require access to the activated chip as well for validating the attack. In the case of FSM obfuscation, structural and topological analysis means that the attacker can find the state registers in locked netlist. This step is a prerequisite for re-constructing the STG. The authors of [31] utilized fundamental properties of the state registers, e.g., register type, strongly connected components, combinational logic feedback paths, dependency, and control behavior metric to distinguish the state registers. This approach aided them in reverse-engineering several state-of-the-art FSM obfuscation schemes. One of the key observation from Fig. 2 as discussed in Section II-D is that, most of the existing FSM obfuscation methods (e.g., HARPOON [30], dynamic state deflection [33], active metering [5]) do not possess any transition from the original states back to the preceding obfuscation states and create a bipartite graph. Hence, the original states do not form a strongly connected component with the obfuscated states according to Tarjan's algorithm [45]. Therefore, obfuscated states along with their associated state registers can be partitioned from the original state registers. ReTrustFSM thwarts such structural and topological analysis-based attacks in the following manner.

- The existing FSM obfuscation methods insert the obfuscated states before the original STG starts and loosely connect them to the original states. However, ReTrustFSM inserts obfuscated states  $(S_0^{Obf}, S_1^{lfsr}, and S_2^{cnt}$  in Fig. 2) deeply rooted into the original FSM at the RTL by following Lemmas 1, 2, and 3. Therefore, in the ReTrustFSM obfuscated circuit, obfuscated states are tightly entangled with the original state machine.

- It can be observed from Fig. 2 that the proposed ReTrustFSM inserts obfuscated states that possess multiple back and forth transitions with the original states. Hence, the obfuscation states creates a strongly connected component with the original states according to Tarjan's algorithm [45]. Therefore, ReTrustFSM does

$<sup>^{7}\</sup>approx90\%$  accuracy for the prediction of the attack time would be more than enough for the designer to decide about the value of external secrecies (e.g., the difference between actual and predicted would be in the order of a few days while the total de-obfuscation time is in order of few years).

not leave any structural footprint in the obfuscated design that can be exploited by the topological analysis [31].

- The obfuscation circuitry (LFSR, and down-counter) that performs encoding of the postFSM ( $S_3^N$  and optionally  $S_4^N$  in Fig. 2), are initialized by the states of the encFSM ( $S_0^{obf} \rightarrow S_1^{lfsr} \rightarrow S_2^{cnt}$  in Fig. 2) after the traversal of preFSM. Therefore, the obfuscation circuitry in ReTrustFSM are a part of the FSM state registers which makes the search space even larger for structural analysis.

- As implicit secrecy is integrated as part of the operational mode of the encFSM, to mitigate the design vulnerability against the functional analysis-based structural attack [13] (for input pattern checking), stealthy opaque predicate [49] based dynamic secrecy generation has been deployed in ReTrustFSM construction.

Due to the points mentioned above, structural and topological analysis-based attacks [31] are ineffective on the ReTrustFSM obfuscated circuit. It is noteworthy that the circuit will be dysfunctional even if the attacker can reverse engineer the state machine and even distinguish the obfuscated state registers without knowledge of the correct encoding of the original states at RTL. In other words, removing the encFSM and black holes from the STG does not allow the adversary to reconstruct the original FSM, as the encoding of lockedFSM depends on traversal in encFSM.

#### D. REMOVAL ATTACK

In case of a removal attack on ReTrustFSM obfuscated circuitry (LFSR/counter), since a dependency between the obfuscated circuitry and the original functionality is built, the removal of logic dedicated for the obfuscated circuitry results in losing the correct functionality. In such cases, the transition(s) between preFSM to postFSM gets lost, and similar to what demonstrated in Fig. 7, it returns back to the default state,  $S_{init}^N$ . The following is some of the reasons why removal attack does not work on ReTrustFSM:

(i) With access to the netlist and having the basic information of the obfuscation method, the attacker can identify the LFSR/counter in the design and remove them. However, after removing LFSR/counter, the register(s) dedicated for state encoding of the lockedFSM state(s) become *unconnected* (no more connection to LFSR/counter). So, this register, which is part of the FSM circuitry, will be removed during synthesis optimization. This will be followed by removing more parts of the design that are directly connected to this state register. Then with the removal of part of the actual circuit, the removal ultimately corrupts the functionality.

(ii) The functionality of all three obfuscation FSM states is clearly defined and based on the threat model, the adversary has access to the locked gate-level netlist. However, in oracle, a sub-set of registers, including state registers, and LFSR/counter registers are not directly available. So, the adversary has to apply stimuli to primary inputs and observe primary outputs. In this case, there exists no connection between PI/PO pairs and the specification of internal registers as they are not observable. The adversary cannot distinguish between the state registers vs. the other registers. So, the removal of these three states needs a prerequisite in which the adversary must apply methods like Tarjan to see if they are able to distinguish between registers. To the best of our knowledge, there is no mechanism that can distinguish between these registers by 100% (guaranteed) success ratio [31], [38]. When the adversary cannot distinguish state registers, applying input patterns for re-constructing the whole STG, and then based on the whole STG (for detecting and removal of three obfuscation states) becomes clueless.

#### E. FUNCTIONAL CORRUPTIBILITY-GUIDED ATTACK

As discussed in Section II-C, functional corruptibility-guided SAT attack (Fun-SAT) [29] is an extended version of BMC (SAT) attack, in which the required minimum numbers of unrolling for de-obfuscation is estimated based on output corruptibility. Then, based on the number of unrolling, the satisfiability is invoked. Hence, to perform this attack, the adversary must have PI/PO access to the (1) activated chip (oracle), and (2) gate-level netlist. Fun-SAT attack [29] analyzes the keyless FSM obfuscation method [30] to estimate the minimum number of unrolling such that the functional equivalency between the unrolled circuit and the original sequential circuit is 100%. Once Fun-SAT deciphers the minimum number of required unrolling, it unrolls the obfuscated circuit and performs the regular SAT attack [9] to extract the secret enabling key ({ $I_{en}, I_{auth}$ }).

Although Fun-SAT efficiently works on a set of FSM obfuscation techniques that rely on implicit external secrecy, e.g., HARPOON [30], the corruptibility analysis fails to build the functional equivalency between the unrolled circuit and the original sequential circuit once explicit secrecy is in place, as without the correct external secrecy, there exists no equivalency between the obfuscated and the original circuit. Since ReTrustFSM is a hybrid approach with a strong correlation between implicit and explicit secrecy, Fun-SAT fails to break ReTrustFSM obfuscated circuit because the corruptibility analysis does not provide any advantage. The attack eventually reduces to a regular SAT or BMC attack, the analysis and results of which are presented in Section IV-A and V. Additionally, in ReTrustFSM, the obfuscated states are deeply twisted as an intermediate region with the original FSM. So, any pre-processing like corruptibility analysis that helps to reveal the required number of unrolling is not applicable on ReTrustFSM obfuscated circuits.

#### F. ORACLE-LESS MACHINE-LEARNING ATTACK

Oracle-less ML-based attacks on logic locking, e.g., SWEEP attack [52], rely on re-synthesizing the locked gate-level netlist with additional key-gates and then learning the optimization algorithm of the EDA tool. So, the adversary only require access to the locked gate-level netlist for applying the key value followed by re-synthesis. With the knowledge of

the re-synthesis-based optimization algorithm, the SWEEP attack then tries to revert to the original gate-level netlist before locking. These ML-based attacks [52], [60] focus on tracking down certain key gates, e.g., XOR, XNOR, or MUX [6], [10]. Therefore, locking methods that depend on specific key gates are extremely susceptible to these oracle-less attacks. Additionally, almost all ML-based attacks build their knowledge based on *guess and check* method, in which the guessing is always around the value for the explicit secrecy. Hence, in cases where implicit secrecy is in place, such attacks become ineffective.