## DAG Scheduling in the BSP Model

Pál András Papp Computing Systems Lab Huawei Zurich Research Center pal.andras.papp@huawei.com Georg Anegg Computing Systems Lab Huawei Zurich Research Center georg.anegg@huawei.com A. N. Yzelman Computing Systems Lab Huawei Zurich Research Center albertjan.yzelman@huawei.com

## **ABSTRACT**

We study the problem of scheduling an arbitrary computational DAG on a fixed number of processors while minimizing the makespan. While previous works have mostly studied this problem in relatively restricted models, we define and analyze DAG scheduling in the Bulk Synchronous Parallel (BSP) model, which is a well-established parallel computing model that captures the communication cost between processors much more accurately. We provide a detailed taxonomy of simpler scheduling models that can be understood as variants or special cases of BSP, and discuss the properties of the problem and the optimum cost in these models, and how they differ from BSP. This essentially allows us to dissect the different building blocks of the BSP model, and gain insight into how each of these influences the scheduling problem.

We then analyze the hardness of DAG scheduling in BSP in detail. We show that the problem is solvable in polynomial time for some very simple classes of DAGs, but it is already NP-hard for in-trees or DAGs of height 2. We also separately study the subproblem of scheduling communication steps, and we show that the NP-hardness of this problem can depend on the problem parameters and the communication rules within the BSP model. Finally, we present and analyze a natural formulation of our scheduling task as an Integer Linear Program.

## **CCS CONCEPTS**

Theory of computation → Parallel computing models; Problems, reductions and completeness.

## **KEYWORDS**

Directed acyclic graph, bulk synchronous parallel, scheduling, NP-complete, Integer Linear Programming

## 1 INTRODUCTION

The optimal scheduling of complex workloads is a fundamental problem not only in computer science, but also in various other fields such as logistics and operations research. In a computational context, one of the most natural applications of scheduling is when we have a complex computation consisting of various different subtasks, and we want to execute this computation on a parallel (multi-processor or multi-core) architecture, while minimizing the total time required for this. Unsurprisingly, this question has been extensively studied already since the 1970s, and has gained even more importance in the past decade with the widespread use of manycore architectures.

In these scheduling problems, a computational task is represented as a Directed Acyclic Graph (DAG), where each node corresponds to a computational step or subtask, and each directed edge (u,v) represents a dependency relation, i.e. that the processing of node u has to be finished before the processing of node v begins, since the output of operation u is required as an input for operation v. This DAG model of general computations is not only prominent in scheduling, but also in many further topics such as pebbling, which studies time-memory tradeoffs in a given computation.

However, from a complexity-theoretic perspective, the scheduling of general DAGs is already a hard problem even in very simple settings, e.g. even in models that heavily simplify or completely ignore the communication costs between processors, which is known to be the main bottleneck in many computational tasks in practice. Due to this, most theoretical works so far have focused on analyzing the complexity of scheduling in these rather simple models, and while models with more realistic properties were often introduced, the theoretical properties of the scheduling problem in these more realistic models have received little attention.

On the other hand, the parallel computing community has developed far more sophisticated models to accurately quantify the real cost of parallel algorithms in practice. One of the most notable among these is the Bulk Synchronous Parallel (BSP) model, which is still relatively simple, but provides a delicate cost function which also captures the volume of communicated data and the synchronization costs in a given parallel schedule. BSP (and other such models) are fundamental tools to evaluate and compare parallel algorithms, both in theoretical works and in concrete practical implementations. However, previous theoretical works on BSP mostly focus on finding and analyzing parallel schedules for a specific algorithm, and they do not study BSP as a model for scheduling general DAGs, i.e. an arbitrary computational task.

Our goal in this paper is to bridge this gap between theory and practice to some extent, and understand the fundamental theoretical properties of the DAG scheduling problem in the BSP model. The more detailed cost function of BSP naturally results in an even more complex scheduling problem; on the other hand, understanding the key properties of this problem is crucial, since it provides a more accurate model to evaluate parallel schedules for general computations in practice.

More specifically, our main contributions are as follows:

(i) We first define the DAG scheduling problem in the BSP model. We then provide a taxonomy of scheduling models from previous works, and show that many of these can be understood as a special case of BSP; as such, analyzing the relations between these models can essentially allow us to gain insight into how each of the different aspects of the BSP model affects the scheduling problem. We also discuss several slightly different variants of the BSP model; our following results indicate that even

1

- seemingly small changes in the model definition may have a significant effect on the theoretical properties of the model.

- (ii) We then analyze the complexity of the BSP DAG scheduling problem, with the goal of understanding when (i.e. for which kind of DAGs) the problem becomes NP-hard. In particular, our results show that BSP scheduling is still solvable in polynomial time for simple DAGs that consist of several connected chains, but it is already NP-hard for slightly more complex classes of DAGs, such as in-trees or DAGs of height 2.

- (iii) We separately analyze the subproblem of scheduling communication steps, assuming that the assignment of tasks to processors and so-called supersteps is already fixed. We show that in several variants of the BSP model, this subproblem of finding the optimal communication schedule is already NP-hard.

- (iv) Finally, we present a natural formulation of the BSP scheduling task as an Integer Linear Programming (ILP) problem; this provides a simple approach in practice to find the optimal BSP schedules for smaller DAGs using ILP solvers. We analyze and compare the number of variables and constraints required for such a formulation in different variants of the model.

We note that our technically most involved contributions correspond to points (ii) and (iii) above; however, in the main part of the paper, we instead put more focus on point (i), in order to provide more intuition on the behavior and properties of the models.

## 2 RELATED WORK

Scheduling is one of the most fundamental problems of computer science, and has been studied extensively since the 1970s. DAGs are one of the most common models for such problems, since in various applications, the subtasks or computational steps have precedence relations between them (subtask v can only be started after another subtask v has been finished). Since we focus on BSP, we assume in the paper that our DAG corresponds to a computational task.

The first results on DAG scheduling considered a simple setting where communication between the processors is free, which essentially corresponds to the PRAM model. The numerous results in this model include a line of polynomial algorithms for P=2 processors [5, 10, 42], polynomial algorithms for special classes of DAGs (but P>2) [6, 7, 11], hardness results for the  $P=\infty$  case [3, 23, 46], and a range of results for weighted DAGs [4, 22, 34]. The results on some of these topics, e.g. approximation algorithms, are still rapidly improving in recent years [13, 26, 28, 44]. On the other hand, some basic questions are still open even in this fundamental model: for instance, it is still not known whether scheduling for some fixed P>2 is NP-hard.

A more realistic version of this model was introduced in the late 1980s [37, 50], where there is a fixed communication delay between processors. Related work has also explored numerous algorithms and hardness results in this setting, in particular for the case of unit-length delays [16, 18] or infinitely many processors [18, 30, 35]. The approximability of the optimal solution is also a central question in this model that has been receiving significant attention even in recent years [21, 29].

This communication delay model is still unrealistic in the sense that it allows an unlimited amount of data to be communicated in any single time unit. To our knowledge, the only more sophisticated DAG scheduling model which measures communication volume is the recently introduced single-port duplex model [36]. However, this model has not been studied thoroughly from a theoretical perspective, and it also has the drawback that in contrast to BSP, it cannot be extended by some real-world aspects such as synchronization costs.

We describe the scheduling models above in more detail in Section 4. We note that there are also numerous extensions of these problem models with further properties, such as heterogeneous processing units, jobs that require several processing units, or separate deadlines for given tasks [24, 25, 27, 45].

On the other hand, BSP has been introduced as a prominent model of parallel computing in 1990 [47], and studied extensively ever since [2, 31, 43]. The model has also found its way into various applications, most notably through the BSPlib standard library [17] and its different implementations [51, 52]. Further fundamental results on BSP include the analysis of prominent algorithms in this model [32, 33], as well as the extension of BSP to multi-level architectures [48, 49]. However, to our knowledge, BSP has mostly been used so far to analyze the computational costs of specific parallel implementations of concrete algorithms, as opposed to our work, where we apply it as a general model to evaluate the scheduling of any computational DAG.

## 3 MODELS AND DEFINITIONS

Computational tasks are modelled as a *Directed Acyclic Graph (DAG)* G, with the set of nodes (subtasks) denoted by V, and the set of directed edges (dependencies) by E. We use u and v to denote individual nodes, and n to denote the number of nodes |V|. An edge (u,v) indicates that subtask u has to be finished before the computation of subtask v begins. The *indegree* and *outdegree* of v is the number of incoming and outgoing edges of v, respectively. We will also use [k] as a shorthand notation for the integer set  $\{1, ..., k\}$ .

For scheduling, we assume that we have P identical processors (with P being some fixed constant). Our goal is to execute the computation (all nodes of G) on these P processors in a parallel manner, while minimizing the amount of time this takes, i.e. the time when the last node is executed.

In classical scheduling models, a scheduling is usually an assignment of the nodes to processors  $\pi:V\to [P]$  and concrete time steps  $t:V\to \mathbb{Z}^+$ . The validity conditions on such a schedule (to e.g. satisfy the precedence constraints) are model-dependent; see Section 4.1 for details on specific models. The goal is then to minimize the makespan, i.e.  $\max_{v\in V} t(v)$ .

## 3.1 The BSP model

BSP is a very popular model for the design and evaluation of parallel algorithm implementations. To our knowledge, general DAG scheduling has not been studied in this model before, but extending the interpretation of BSP to this setting is rather straightforward.

3.1.1 Overview. In contrast to classical models where nodes are assigned to concrete points in time, the BSP model instead divides the

execution of nodes into larger batches, so-called *supersteps*. Each superstep consists of two phases, in the following order:

- 1. *Computation phase*: each processor may execute an arbitrary number of computation steps, but no communication between the processors is allowed.

- 2. *Communication phase*: processors can communicate an arbitrary number of values to each other, but no computation is executed.

The main motivation behind these supersteps is to encourage executing the necessary communications in large blocks, because in practice, inter-processor communication often comes with a large fixed cost (e.g. synchronization or network initialization) that is independent from the data volume, and hence it is desired to have as few communication phases as possible.

- 3.1.2 *Formal definition.* Formally, this means that a *BSP schedule* with a given number of supersteps *S* consists of:

- An assignment of nodes to processors  $\pi:V\to [P]$  and to supersteps  $\tau:V\to [S]$ . For simplicity, we introduce the notation  $H^{(s,p)}$  for the set of nodes assigned to processor p and superstep s, i.e. all  $v\in V$  with  $\pi(v)=p$ ,  $\tau(v)=s$ . We can imagine the nodes of  $H^{(s,p)}$  to be executed in an arbitrary (but topologically correct) order on p in superstep s.

- A set  $\Gamma$  of 4-tuples  $(v, p_1, p_2, s) \in V \times [P] \times [P] \times [S]$ , indicating that the output of node v is sent from processor  $p_1$  to processor  $p_2$  in the communication phase of superstep s. In this base variant of the BSP model, we only include  $p_1$  in these 4-tuples for clarity, but we always assume  $p_1 = \pi(v)$ , i.e. the value is sent from the processor where it was computed.

A valid BSP schedule must satisfy the following conditions:

- (i) A node v can only be computed if all of its predecessors are available, i.e. they were either computed on the same processor in an earlier (or the same) superstep, or sent to that processor before the given superstep. That is, for all  $(u,v) \in E$ , if  $\pi(u) = \pi(v)$  then we must have  $\tau(u) \le \tau(v)$ , and if  $\pi(u) \ne \pi(v)$  then we must have  $(u, \pi(u), \pi(v), s) \in \Gamma$  for some  $s < \tau(v)$ .

- (ii) Communication steps in  $\Gamma$  can only send already computed values; that is, if  $(v, p_1, p_2, s) \in \Gamma$ , then  $p_1 = \pi(v)$ , and  $\tau(v) \le s$ .

- 3.1.3 Cost function. The cost of a superstep is defined as follows. The computation phase can be executed in parallel on the different processors, so its cost (the amount of time it takes) in superstep  $s \in [S]$  is the largest amount of computation executed on any of the processors. More formally, the *work cost* of superstep s (first for a given processor  $p \in [P]$ , and then in general) is defined as

$$\begin{aligned} C_{work}^{(s,p)} &= |H^{(s,p)}|, \\ C_{work}^{(s)} &= \max_{p \in [P]} C_{work}^{(s,p)}. \end{aligned}$$

Communication costs, on the other hand, are governed by two further global problem parameters:  $g \in \mathbb{N}$  is the cost of communicating a single unit of data, and  $L \in \mathbb{N}$  is the fixed latency cost incurred by each superstep. BSP assumes that different values can be communicated in parallel in general, but any processor can only send and receive a single value in a single time unit. As such, BSP defines a *send* and *receive cost* as the number of values sent and received, respectively, by processor p in superstep s, and then the

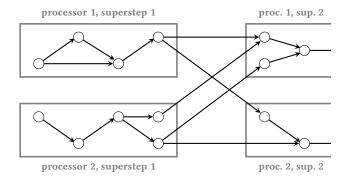

Figure 1: Illustration of an example BSP schedule for a DAG. Note that the labelled boxes in the figure only represent the computation phase of a given superstep; the superstep itself consists of this computation phase, and also the communication phase that follows.

communication cost of a superstep (for p, or in general) is the maximum of these values; this cost function is also known as h-relation. More formally:

$$\begin{split} C_{sent}^{(s,p)} &= |\{(v,p_1,p_2,s_1) \in \Gamma \mid p_1 = p, s_1 = s\}|, \\ C_{rec}^{(s,p)} &= |\{(v,p_1,p_2,s_1) \in \Gamma \mid p_2 = p, s_1 = s\}|, \\ C_{comm}^{(s,p)} &= \max(C_{sent}^{(s,p)}, C_{rec}^{(s,p)}), \\ C_{comm}^{(s)} &= \max_{p \in [P]} C_{comm}^{(s,p)}. \end{split}$$

The cost  $C^{(s)}$  of superstep s and the cost C of the entire schedule is then defined through the sum of these terms:

$$\begin{split} C^{(s)} &= C_{work}{}^{(s)} + g \cdot C_{comm}{}^{(s)} + L\,, \\ C &= \sum_{s \in [S]} C^{(s)}\,. \end{split}$$

For a concrete example, consider the BSP schedule illustrated in Figure 1, and let s=1,  $p_1=1$ ,  $p_2=2$ . Here processor  $p_1$  computes 4 nodes, and processor  $p_2$  computes 5 nodes, so  $C_{work}^{(s,p_1)}=4$ ,  $C_{work}^{(s,p_2)}=5$ , and  $C_{work}^{(s)}=\max(4,5)=5$  in the computation phase. In the communication phase,  $p_1$  must send a single value to  $p_2$  (so  $C_{sent}^{(s,p_1)}=C_{rec}^{(s,p_2)}=1$ ), while  $p_2$  must send two values to  $p_1$  ( $C_{sent}^{(s,p_2)}=C_{rec}^{(s,p_1)}=2$ ). This implies  $C_{comm}^{(s,p_1)}=C_{comm}^{(s,p_2)}=\max(2,1)=2$ , and hence  $C_{comm}^{(s)}=2$ . The total cost of the superstep is  $C^{(s)}=5+2\cdot g+L$ .

For a more detailed discussion on the design and specific ingredients of the BSP model, we refer the reader to [2, 31].

3.1.4 As a scheduling problem. These definitions already allow us to formally define the DAG scheduling problem in the BSP model.

Definition 3.1. Given an input DAG, the goal of the BSP scheduling problem is to find a feasible BSP schedule  $(\pi, \tau, \Gamma)$  as described above, with minimal cost C.

In the decision version of the problem, we also have a maximal cost parameter  $C_0$ , and we need to decide whether there is a BSP schedule with cost  $C \le C_0$ . For simplicity, we will often focus on

the simpler case of L=0, which is already rather similar to the general version of  $L\geq 0$  in terms of hardness.

From a complexity theory perspective, it is important to note that we consider the parameters P, g, L to be small fixed constants (properties of our computing architecture), and not parts of the problem input. We especially emphasize this for P, since in contrast to our work, some other works assume that P is an input variable that can be up to linear in n; however, this is unrealistic in most applications, and also makes the problem unreasonably hard even for trivial DAGs. In general, both settings (fixed P and variable P) have been extensively studied before, and are distinguished by "Pm" and "P" in the classical 3-field notation.

We also point out that the number of supersteps S is not a parameter of the problem, and can be freely chosen by a scheduling algorithm; we only used it above because the problem definition is easier to present for a fixed S.

#### 3.2 Further model extensions

There are also several simple generalizations of scheduling models that occur frequently in the literature, extending the problem with further real-world aspects. Most of our results will focus on the base model described above, but we occasionally also highlight how our observations carry over to these extended models.

3.2.1 Work and communication weights. Real-world computations often consist of subtasks with varying computational requirements. Hence one very natural extension of this setting is to also assume a work weight function  $w_{work}:V\to\mathbb{Z}^+$  that defines the amount of time required to execute each node. Similarly to other works, we assume for simplicity that these weights are integers. Most scheduling models are easy to extend with these work weights: e.g. in case of our BSP, the work cost of a superstep is then understood as the sum of node weights in the superstep, i.e.  $C_{work}^{(p,s)}=\sum_{v\in H^{(s,p)}} w_{work}(v)$ .

Besides heterogeneous work weights, the size of the output data of nodes can also differ significantly, and hence it can take a different amount of time to communicate specific values between the processors. As such, another extension is to assume *communication weights*  $w_{comm}: V \to \mathbb{Z}^+$  which describe the data size (e.g. number of bytes) to be communicated in case of each node (alternatively, some works consider this to be a function  $w_{comm}: E \to \mathbb{Z}^+$ ; we discuss this in Section 5). The communication cost can then also be adjusted accordingly, by multiplying each term in  $C_{sent}$   $^{(s,p)}$  and  $C_{rec}$   $^{(s,p)}$  by the respective  $w_{comm}(v)$  weight.

3.2.2 Duplication. Our definitions above assign every computational task to a single processor and time step. However, many works also allow duplication (also called replication), i.e. to execute the same node multiple times, on different processors. Formally, a schedule in this case becomes a function  $\tau: V \times [P] \to \mathbb{Z}^+ \cup \{\emptyset\}$  such that for all  $v \in V$  there exists a  $p \in [P]$  with  $\tau(v,p) \neq \emptyset$ . Naturally, these duplication steps come with more total time spent on computation, but on the other hand, they can reduce the required amount of communication between the processors, hence decreasing the scheduling cost altogether (see Section 4.4 for examples).

#### 4 COMPARISON TO OTHER MODELS

## 4.1 Taxonomy of simpler models

In the most basic scheduling model, which we call classical scheduling, nodes are assigned to processors  $\pi:V\to [P]$  and time steps  $t:V\to \mathbb{Z}^+$ , with two conditions for correctness: we cannot execute two nodes on the same processor at the same time  $(\nexists u,v\in V)$  with  $\pi(u)=\pi(v)$ , t(u)=t(v), and we must respect the precedence constraints  $(\forall (u,v)\in E)$  we need t(u)< t(v). The cost of a schedule is simply its makespan  $\max_{v\in V} t(v)$ . Since there are no communication costs between the processors, this setting can be understood as scheduling in a simple PRAM model.

A slightly more realistic version of this setting also considers communication delays between processors; we will refer to this as the *commdelay model*. This model has an additional input parameter g, and it is only different in the second validity constraint: for all  $(u,v) \in E$ , if  $\pi(u) = \pi(v)$ , then it still requires t(u) < t(v), but if  $\pi(u) \neq \pi(v)$ , then we now need to have t(v) > t(u) + g.

Note that BSP has two significant differences from this commdelay model. On the one hand, commdelay allows a processor p to execute a computation and a communication simultaneously, while in BSP, these are explicitly separated into a computation / communication phase. On the other hand, commdelay in fact allows any number of values to be sent from  $p_1$  to  $p_2$  simultaneously, whereas BSP also considers the communication volume: sending k values from  $p_1$  to  $p_2$  takes k times as long as sending only a single value.

Previous work has already briefly considered the extension of the commdelay model with both of these modifications separately:

- The work of [9] considers a variant of commdelay where computation and communication can only happen in separate phases. The paper proves several hardness results in this model, and in particular, it studies how a standard commdelay schedule can be transformed into this commdelay model with phases.

- The work of [36] introduces the so-called *single-port duplex* (SPD) model, which extends commdelay with the measuring of communication volume: in particular, besides the assignment  $t:V\to\mathbb{Z}$ , the schedule must also assign the communication of any value from  $p_1$  to  $p_2$  to a concrete time step, and each processor can only send or receive a single piece of data in each time unit (see Appendix A or [36] for more details).

The models discussed above are summarized in Table 1 according to how they capture communication costs, and whether they allow computation and communication simultaneously. The table shows that DAG scheduling in the BSP model indeed fills a natural place in this taxonomy of models, which further indicates that our interests in its properties is well-justified. Furthermore, comparing specific results for BSP and for simpler models in this table allows us to gain further insight into how specific aspects of the model affect the properties of the scheduling problem.

There is a further technical question that arises regarding the data volume-aware models in the last column of this table. In SPD, each data transfer is assigned to a specific time step, whereas in BSP, we define communication costs through the simpler notion of h-relations. It is a natural question whether these two methods indeed describe the same communication cost function (for L=0 in BSP). That is, to justify the use of h-relations, we need to show that

4

|                                     | free communication (no cost)            | simplified comm. cost<br>(any amount of data<br>in a single step) | exact comm. cost<br>(cost depends on<br>data volume) |

|-------------------------------------|-----------------------------------------|-------------------------------------------------------------------|------------------------------------------------------|

| comp. & comm.<br>simultaneously     | classical<br>scheduling<br>[5, 28, 42,] | commdelay<br>[21, 37, 50,]                                        | single-port duplex<br>[36]                           |

| comp. & comm.<br>in separate phases | classical<br>scheduling<br>[5, 28, 42,] | commdelay<br>with phases<br><sup>[9]</sup>                        | BSP<br>[novel for DAGs]                              |

Table 1: Simplified taxonomy of DAG scheduling models. The horizontal axis shows different models of capturing the communication cost, whereas the vertical axis shows if simultaneous execution of computation and communication steps is allowed.

if each processor p is sending and receiving  $C_{sent}{}^{(s,p)}$  and  $C_{rec}{}^{(s,p)}$  values, respectively, then these communications steps can indeed be scheduled into  $C_{comm}{}^{(s)}$  time steps according to the rules of the SPD model, i.e. such that each processor only sends and receives a single value in each step. Fortunately, this is rather straightforward with standard graph-theoretic tools, by decomposing a bipartite multigraph on P+P nodes into perfect matchings.

LEMMA 4.1. If every processor sends and receives at most C values in a communication phase, then it can be scheduled into C time slots.

However, the same question is more technical with communication weights; we show that in this case, the lemma does not hold if the communication steps cannot be split into smaller parts.

## 4.2 Separation and synchronization

When studying the last column of Table 1, one can observe that the difference between SPD and BSP is, in fact, twofold. On the one hand, BSP assumes that at any point in time, a processor can only do either computation or communication, but not both (e.g. because the flow of communication is controlled by the same processing unit that executes computation). On the other hand, BSP assumes that the whole computation is divided into supersteps, which is also called *barrier synchronization*: in order to communicate a value v, we first need a point in time when none of the processors are executing any computations, and hence they can initialize the communication process. These global synchronization points then naturally divide the execution into supersteps, and only allow processors to communicate values that were already available before the last synchronization point.

If we separate these two properties from each other, we can extend our taxonomy into Table 2, which includes further model variants that are closely related to BSP. We briefly discuss these models below, with the details deferred to Appendix A.

First consider the case when global synchronization is still required, but processors are free to compute and communicate simultaneously. In fact, the original definition of BSP by Valiant [47] corresponds to this setting: the cost of a superstep was defined as

$$C^{(s)} = \max \left( C_{work}^{(s)} , g \cdot C_{comm}^{(s)} + L \right),$$

hence implicitly assuming that the computations and communications of superstep s can happen simultaneously. We will refer to

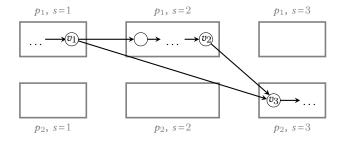

Figure 2: Example for interpreting DAG scheduling in the maxBSP model (with only some of the nodes shown).

this model as *maxBSP*. In contrast to [47], other works, including recent textbooks on BSP [2], apply the definition in Section 3.1.2, where  $C_{work}^{(s)}$  and  $g \cdot C_{comm}^{(s)} + L$  are summed up to obtain  $C^{(s)}$ .

However, the interpretation of maxBSP for DAG scheduling requires some consideration. In the example in Figure 2,  $v_2$  needs to be the last node to be computed on processor  $p_1$  in superstep 2, and  $v_3$  must be the first node to be computed on  $p_2$  in superstep 3; this shows that the communication phase of superstep 2 (sending  $v_2$  from  $p_1$  to  $p_2$ ) cannot happen simultaneously with the computation phase of either superstep 2 or 3. As such, simply applying the maxBSP cost function leads to an inaccurate model.

For a reasonable model, we also need to consider which computations and communications can happen at the same time. For instance,  $v_1$  is already computed in superstep 1, and only required in superstep 3, so it can indeed happen simultaneously with the computations in superstep 2. In general, DAG scheduling in maxBSP means that each superstep s consists of a simultaneous computation and communication phase, and we can only send a value v from  $p_1$  to  $p_2$  if v was computed on v in superstep v in superstep v in superstep v in superstep v in after.

On the other hand, consider the case when a processor can only do either computation or communication at a given point in time, but no global synchronization is required between the processors. Intuitively, this setting allows e.g. two processors  $p_1$  and  $p_2$  to stop computation and exchange several values with each other, while the rest of the processors carry on computing other nodes in the meantime. One can interpret this case as the so-called  $\alpha - \beta$

|                                 |            | free communication (no cost) | simplified comm. cost<br>(any amount of data<br>in a single step) | exact comm. cost<br>(cost depends on<br>data volume) |

|---------------------------------|------------|------------------------------|-------------------------------------------------------------------|------------------------------------------------------|

| comp. & comm.<br>simultaneously | no<br>sync | classical<br>scheduling      | commdelay                                                         | single-port duplex                                   |

|                                 | sync       | classical<br>scheduling      | commdelay<br>with sync points                                     | maxBSP                                               |

| comp. & comm.<br>separately     | no<br>sync | classical<br>scheduling      | $\alpha - \beta$ with $\beta = 0$ (or subset-CD)                  | $\alpha - \beta$ with $\alpha = 0$ (or subset-BSP)   |

|                                 | sync       | classical<br>scheduling      | commdelay<br>with phases                                          | BSP                                                  |

Table 2: Extended table of DAG scheduling models. The vertical axis is split according to two properties: (i) whether computation and communication are allowed simultaneously, and (ii) whether barrier synchronization is required for communication.

model [41] with a choice of  $\alpha=0$ , although this concept is often used as only a cost function (instead of a complete model), and hence its definition varies across different works. Alternatively, we could assume that barrier synchronization is still required, but only among the subset of nodes that are actually communicating, thus creating a  $(p_1, p_2)$ -specific communication phase. This model variant, sometimes called subset-BSP, was also discussed before to analyze whether barrier synchronization is indeed a key property of the BSP model [15, 40].

As shown in Table 2, we can also apply the same separation idea to obtain 4 slightly different variants of the commdelay model. We briefly define and discuss these in Appendix A for completeness. In contrast to this, classical scheduling remains identical in all these cases, since communications take no time here, and as such, all integer points in time can be used for synchronization.

We note that all models with barrier synchronization can be naturally extended with a latency parameter L similarly to BSP.

## 4.3 Optimum cost in different models

One of the most natural questions regarding this taxonomy is how the optimum costs in these different models relate to each other in a given DAG. Firstly, note that in any of the models, one of the processors must have a work cost of  $\frac{n}{P}$  at least; this provides a lower bound on the optimum in all cases. On the other hand, in each model, executing the entire DAG on a single processor (without communication) always provides a viable solution of cost n.

PROPOSITION 4.2. We have  $\frac{n}{P} \leq OPT \leq n$  in each of these models, with OPT denoting the optimum cost.

This also shows that the trivial solution of using only a single processor is a factor P approximation of the optimum in any of these models. The same argument naturally carries over to the case of work weights if we replace n by  $\sum_{v \in V} w_{work}(v)$ .

Next we compare the optimum cost in the two fundamental models, classical scheduling and commdelay, to the BSP optimum (denoted by  $\mathrm{OPT}_{class}$ ,  $\mathrm{OPT}_{CD}$  and  $\mathrm{OPT}_{BSP}$ , respectively, assuming L=0 in BSP). We clearly have  $\mathrm{OPT}_{class} \leq \mathrm{OPT}_{CD} \leq \mathrm{OPT}_{BSP}$ ; however, finding the maximal difference is more involved.

LEMMA 4.3. For any DAG and parameters P and g, we have

- $OPT_{CD} \leq \min(1 + g, P) \cdot OPT_{class}$ ,

- $OPT_{BSP} \leq P \cdot OPT_{class}$ ,

- $OPT_{BSP} \leq P \cdot OPT_{CD}$ .

For each case, there is a DAG construction where this bound is essentially tight: we show matching lower bounds of both P and  $(1+g-\varepsilon)$  (for any  $\varepsilon>0$ ) in the first case, and a matching lower bound of P in the second and third cases.

The proof of the lemma is discussed in Appendix B. Intuitively, the worst case between  $\mathrm{OPT}_{class}$  and  $\mathrm{OPT}_{CD}$  is when we are forced to communicate a new value after every computation step, thus increasing  $\mathrm{OPT}_{class}$  by a (1+g) factor. For BSP, a similar construction can result in such a high communication cost that it is simply more beneficial to execute the entire DAG on a single processor, reaching the maximal difference from Proposition 4.2.

Due to our focus on BSP, we also analyze the relation between the models in the last column of Table 2 in detail. We denote their optimum costs by  $\mathsf{OPT}_{SPD}$ ,  $\mathsf{OPT}_{mBSP}$ ,  $\mathsf{OPT}_{\beta}$ ,  $\mathsf{OPT}_{BSP}$  from top to bottom, again for L=0. The restrictiveness of the models implies  $\mathsf{OPT}_{SPD} \leq \mathsf{OPT}_{mBSP} \leq \mathsf{OPT}_{BSP}$  and  $\mathsf{OPT}_{SPD} \leq \mathsf{OPT}_{\beta} \leq \mathsf{OPT}_{BSP}$ . We complement this by the following observations.

Theorem 4.4. For any DAG and parameters P and g, the optimum cost between any two of the models in the last column of Table 2 can differ by a factor 2 at most, or equivalently, we have

$$OPT_{BSP} \leq 2 \cdot OPT_{SPD}$$

.

Furthermore, we present DAG constructions that prove

- an essentially matching lower bound of  $(2 \varepsilon)$  on the difference for the cases  $(OPT_{SPD} \leq OPT_{\beta})$ ,  $(OPT_{SPD} \leq OPT_{BSP})$ ,  $(OPT_{mBSP} \leq OPT_{\beta})$  and  $(OPT_{mBSP} \leq OPT_{BSP})$ ,

- a slightly looser lower bound of  $(\frac{3}{2} \varepsilon)$  on the difference for the cases  $(OPT_{SPD} \leq OPT_{mBSP})$ ,  $(OPT_{\beta} \leq OPT_{mBSP})$  and  $(OPT_{\beta} \leq OPT_{mBSP})$

*for any*  $\varepsilon > 0$ .

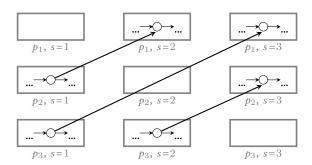

Figure 3: Example DAGs with work weights in the classical scheduling model with barrier synchronization, for P=3. The weights are only shown for nodes of non-unit weight.

## 4.4 Further properties

We discuss a few further properties of the models. Firstly, while all cells in the first column of the table seem identical, even this classical setting becomes more interesting if we have work weights.

Proposition 4.5. In classical scheduling with work weights, barrier synchronization can increase the optimum cost.

PROOF SKETCH. Consider the weighted DAG in Figure 3a with P=3 processors; this can easily be scheduled in 5 timesteps in the classical setting. However, when barrier synchronization is required, the same DAG will have an optimal makespan of 6 in classical scheduling: since no communication is allowed while the task of weight 3 is being processed, it is not possible use the other two processors to parallelize the upper branch of the DAG.

The same construction idea can also be generalized to show a factor 2 difference between the optimum costs. Hence in case of weighted DAGs, barrier synchronization can make a significant difference even in the classical model.

Another natural question is the role of duplication in this taxonomy: in which of these models can it reduce the optimum cost?

Proposition 4.6. Duplication can reduce the optimum cost

- in all models with communication cost (middle and right-hand column of Table 2),

- in the classical scheduling model with barrier synchronization, but only if we have work weights.

Proof sketch. For the first point, consider a simple DAG consisting of two directed paths of length  $\ell$ , and a common source node  $v_0$  that has an edge towards the initial node of both paths. Without duplication, the optimal schedule assigns the two paths to  $p_1$  and  $p_2$ , and the source node to, say,  $p_1$ ; this has a work cost of  $\ell+1$  and communication cost  $1\cdot g$  in all of these models. On the other hand, if  $v_0$  is duplicated on both  $p_1$  and  $p_2$ , then no communication is required, and the total cost is only  $\ell+1$ .

In classical scheduling without work weights, duplication cannot help, since after each time step, the computed values can be freely distributed to all processors without cost. However, consider the weighted DAG of Figure 3b with P=3. Classical scheduling without synchronization allows a makespan of 5 here. If synchronization is required, then due to the weight-2 nodes on the critical paths, it is not possible to send a value (the grey node) at t=2 or t=3, and hence the best makespan becomes 6. However, if instead we can duplicate the grey node on two processors, then we can avoid this problem, and again obtain a makespan of 5.  $\Box$

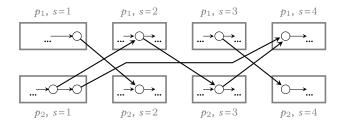

Figure 4: Example BSP schedule where free data movement allows a lower communication cost than direct data transfer.

## 5 COMMUNICATION MODELS WITHIN BSP

In the rest of the paper, we focus on the BSP model. However, even within BSP, there are several different options to model the communication rules; while these are seemingly small changes in the model definition, we will see that they can have a significant effect on the properties of the model. We provide a more formal definition of each of these variants in Appendix A.

Free movement of data. Recall that for simplicity, our base BSP model assumed  $\pi(v) = p_1$  for all  $(v, p_1, p_2, s) \in \Gamma$ , i.e. values are always sent from the processor where they were computed. In practice, there is no reason to make this restriction; in order to transfer a value from  $p_1$  to  $p_2$ , one might as well send it from  $p_1$  to a third processor  $p_3$  first, and then from  $p_3$  to  $p_2$ .

Moreover, there are simple examples where this indeed results in a lower communication cost altogether. Consider the BSP schedule in Figure 4 with P=3 processors. This schedule has a node that is computed on  $p_3$  in superstep 1, but later only needed on  $p_1$  in superstep 3. In case of direct transfer, we can send this value from  $p_3$  to  $p_1$  in either superstep 1 or 2; however,  $p_1$  must already receive a value in superstep 1, and  $p_2$  must already send a value in superstep 2, so both of these choices increase the communication cost in one of the supersteps. On the other hand, with free data movement, we can send the value from  $p_3$  to  $p_2$  in superstep 1, and then from  $p_2$  to  $p_1$  in superstep 2, without increasing the communication cost in either superstep. Thus allowing unrestricted movement of data between the processors can indeed lead to better solutions.

Singlecast or broadcast. Another interesting question is what happens if processor p wants to send a single value v to multiple other processors  $p_1,...,p_k$  in the same superstep. In our base model, this required a separate entry  $(v,p,p_i,s)$  for all  $i \in [k]$ , and hence contributed k units to the send cost  $C_{send}^{(s,p)}$ . This is a reasonable assumption e.g. if the communication network topology is a fully connected graph; in this case, p needs to send this value over k distinct network links.

On the other hand, there are settings where it is more reasonable to only charge a single unit of send cost for this, or in other words, to assume that data transfers are *broadcast operations*, and hence their values can be received by any number of other processors. This can correspond to e.g. a star-shaped network topology with a single communication device in the middle. While this again seems

7

like a minor modification to the BSP cost function, we will see that it can actually affect several properties of the problem.

Combinations. These two model variations can also be combined with each other to form altogether four different communication models within BSP. We assign abbreviations to each of these models, as shown in Table 3, and we will study several properties of the problem in these models in the next sections.

We also note that these modelling questions only arise in the last column of Table 2; in the commdelay model, these variants are in fact all identical.

Node- or edge-based communication. Finally, we point out that (as per our definitions in Section 3.1) we assume a node-based communication model throughout the paper. That is, each communication step corresponds to sending the output of some node u to another processor, which is then saved on this other processor indefinitely. In particular, if u is computed on  $p_1$ , and it has many outgoing edges  $(u, v_1), ..., (u, v_k) \in E$  to some nodes  $v_1, ..., v_k$  which are all assigned to  $p_2$ , then this only incurs a single communication step in our model. This is in line with several recent works that also assume such a node-based communication model [38, 39].

In contrast to this, some other works (e.g. [36]) assume an edge-based model, where the situation above incurs k distinct communication steps, one for each of the edges  $(u, v_i)$ . This edge-based model might be motivated by a setting where the memory of processors is limited; however, in general, it can overestimate the real communication cost by a factor k.

Note that if we have communication weights, then the natural choice for  $w_{comm}$  is a function  $V \to \mathbb{Z}^+$  in this node-based model. On the other hand, other works assuming an edge-based model sometimes use a function  $w_{comm}: E \to \mathbb{Z}^+$  instead.

## **6 NP-HARDNESS**

Given the DAG scheduling problem in the BSP model, one of the most fundamental questions is its computational hardness. Not surprisingly, it turns out that the problem is NP-hard in general DAGs. However, this raises a natural follow-up question: in which simpler subclasses of DAGs can the problem still be solved in polynomial time, and in which subclasses is it already NP-hard? This question has also received extensive attention in other scheduling models.

The simplest non-trivial subclass of DAGs is so-called *chain DAGs*, where both the indegree and outdegree of each node is upper bounded by 1. This simple subclass of DAGs has been analyzed in several different scheduling models before [8, 45], and in particular, has even been explicitly studied in BSP [14], under slightly different assumptions. Additionally, we also consider a slightly more realistic version of this subclass (in terms of modelling computations): let us say that a DAG is a *connected chain DAG* if it can be obtained by adding an extra source node  $v_0$  to a chain DAG, and drawing an edge from  $v_0$  to the first node of every chain.

We show that for these relatively simple classes of DAGs, the optimal BSP schedule can still be found in polynomial time.

THEOREM 6.1. The BSP scheduling problem can be solved in polynomial time in n for chain DAGs and connected chain DAGs.

The key observation in the proof is that the optimal BSP schedule in chain DAGs always consists of at most P supersteps; this

|                       | Singlecast                                                   | Broadcast                                                       |  |

|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------|--|

| Direct<br>transfer    | DS model  CS: open problem  ILP: $O(n \cdot P \cdot S)$ vars | <b>DB model</b> CS: $NP$ -hard ILP: $O(n \cdot P \cdot S)$ vars |  |

| Free data<br>movement | FS model CS: $NP$ -hard ILP: $O(n \cdot P^2 \cdot S)$ vars   | FB model CS: $NP$ -hard ILP: $O(n \cdot P \cdot S)$ vars        |  |

Table 3: Different communication models within BSP, and a summary of their properties established in Sections 7 and 8.

allows us to find the optimum through a rather complex dynamic programming approach. Adapting the same proof to connected chain DAGs only requires some further technical steps.

On the other hand, it turns out that BSP scheduling already becomes NP-hard in even slightly more complex subclasses of DAGs. In particular, we analyze two further classes of DAGs. On the one hand, we consider DAGs with height only 2, where the *height* of a DAG is defined to be the number of nodes in the longest directed path. On the other hand, we consider *in-trees*, which are DAGs where every node has outdegree at most 1. We show that in these (still relatively simple) classes, the BSP scheduling problem is already NP-hard. Since the scheduling problem is known to be polynomially solvable for these specific classes of DAGs in simpler models [11, 30], this highlights the fact that the more sophisticated cost function of BSP indeed comes at the price of increased computational complexity.

THEOREM 6.2. The BSP scheduling problem is already NP-hard if restricted to DAGs of height 2.

Theorem 6.3. The BSP scheduling problem is already NP-hard if restricted to in-trees.

PROOF SKETCH. The proof of Theorem 6.2 uses a reduction from the k-clique problem, and can be loosely understood as an adaptation of the reduction technique for partitioning in [38] to our BSP scheduling setting. Intuitively, the second level of the DAG consists of gadgets representing each node of the input graph, and we will ensure that at most *k* of these node gadgets can be assigned to  $p_1$  without incurring a too large work cost. The edges of the input graph, on the other hand, are represented by gadgets in the first level of the DAG, and have an edge to both of the incident node gadgets. Each edge gadget will incur communication if one of the corresponding node gadgets is not assigned to  $p_1$ . We use further nodes in the construction to ensure that the cost of these communication steps indeed needs to be summed up, and cannot be parallelized within the h-relation. With the appropriate cost limit  $C_0$ , the construction only admits a valid schedule if there are k nodes in the original graph that form a clique.

The proof of Theorem 6.3 is our most technical proof, requiring P=16 processors; we only provide a brief intuitive overview here. Firstly, our DAG will ensure that in order to keep the cost below  $C_0$ , we can only have  $\frac{n}{D}$  computations on any processor, and

only d communication steps altogether (for some d). The construction then mainly consists of cone gadgets, i.e. nodes  $u_0$  with a very high number of predecessors; these incur a very large communication cost unless (almost) all the predecessors are assigned to the same processor as  $u_0$ . By creating a large cone of size  $\frac{n}{P}$  around  $u_0$  (which occupies a processor for the entire schedule), and drawing further edges from d other cones to this  $u_0$ , we can enforce d separate communication steps, each of them sending a value to  $\pi(u_0)$ , that are unavoidable in any valid schedule. As such, a schedule will need to optimize the cones very carefully to ensure that one of these d values is already available every time when we need to communicate in the DAG. This essentially allows us to ensure that the communication steps can only happen at a given point in time at the earliest.

On the other hand, adding a path of length  $\frac{n}{p}$  to the construction ensures that one of the processors has to compute the next node of this path in every time step. We then attach further predecessors to specific nodes of this path, hence it becomes necessary to split the work between multiple processors to ensure that the *i*-th node of the path is indeed always computed by the *i*-th time step. This essentially allows us to ensure that communications must happen at a given point in time *at the latest*.

The two methods together define the exact time steps when we need to communicate, otherwise we exceed the allowed  $\cos C_0$ . In this setting, we show that there is essentially only one way to develop a valid schedule for our construction. The underlying reduction then uses the 3-partition problem with specific gadgets representing each input number  $a_i$ , and ensures that it is only possible to compute the required nodes by each communication deadline if the numbers  $a_i$  are sorted into triplets that each sum up to a given value.

We note that Theorems 6.1-6.3 apply to any of the BSP communication models in Table 3.

## 7 PROBLEM WITHIN A PROBLEM: COMMUNICATION SCHEDULING

Since *h*-relations are a relatively complex communication cost function in the BSP model, it is natural to wonder if the hardness of BSP scheduling lies only within the assignment of nodes to processors and steps (as in simpler models), or if the scheduling of communication steps also adds another layer of complexity to this. More specifically, assume that the nodes are already assigned to processors and supersteps, but we still need to decide when the values are communicated between the chosen processors; is this subproblem easier to solve?

Definition 7.1. In the communication scheduling (CS) problem, we assume that we are given a fixed  $\pi$  and  $\tau$ , and we need to find a communication schedule  $\Gamma$  that minimizes the resulting BSP cost.

We implicitly assume that  $\pi$  and  $\tau$  are chosen such that there exists a feasible communication schedule, i.e. for all  $(u,v) \in E$ , we have  $\tau(u) \leq \tau(v)$  if  $\pi(u) = \pi(v)$ , and  $\tau(u) < \tau(v)$  if  $\pi(u) \neq \pi(v)$ .

As a heuristic approach, one might consider an eager or lazy communication policy: if some data is computed on processor  $p_1$  in superstep  $s_1$  and required on processor  $p_2$  in superstep  $s_2$ , then we can always send this data immediately in superstep  $s_1$  (eager),

Figure 5: Illustration of the communication scheduling problem: both eager and lazy scheduling are suboptimal. Only a few nodes are shown in each superstep.

or always send it at the latest possible point in superstep  $(s_2-1)$  only (lazy). However, both of these schedules might be suboptimal. Consider the example in Figure 5, where most of the communicated values are immediately needed in the next superstep:  $p_1$  must send a value to  $p_2$  in supersteps 1, 2 and 3, and  $p_2$  must send a value to  $p_1$  in supersteps 1 and 3. However, there is a further value computed by  $p_2$  in s=1, but only needed by  $p_1$  in s=4; we can decide whether to send this value in superstep 1, 2 or 3. The eager and lazy policies send this value in superstep 1 and 3, respectively; however, these both increase the cost of the given h-relation, as  $p_2$  is already sending a value in these supersteps. In contrast to this, sending it in superstep 2 comes at no further cost.

This shows that communication scheduling is indeed an interesting problem on its own. From a theoretical perspective, it is important to understand if the h-relation-based communication cost is, intuitively speaking, complex enough to already make the CS problem NP-hard. From a practical perspective, if CS turns out to be significantly easier to solve, then scheduling heuristics might prefer to first find a good initial BSP schedule for a DAG, and then try to further improve this by fixing the selected  $\pi$  and  $\tau$ , and trying to further reduce the communication cost separately.

Firstly, for the simplest case of only P=2 processors, it turns out that a relatively simple greedy method is already guaranteed to find the optimal solution (in any of the communication models of Table 3, since these are all equivalent for P=2).

Lemma 7.2. The communication scheduling problem can be solved in polynomial time for P = 2 processors.

Interestingly, for general P, it turns out that the properties of the CS problem can heavily depend on the communication model. In particular, we prove that CS is already NP-hard if communication happens according to the DB, FS or FB models. However, the same proof strategy does not work in case of the DS model; we leave it as an open question to future work whether communication scheduling is also NP-hard in DS.

Theorem 7.3. The communication scheduling problem is NP-hard in the DB, FS and FB models.

PROOF SKETCH. The proof uses a reduction from the 3D-matching problem: given three sets X, Y, Z of size N, and a set of M triplets from  $X \times Y \times Z$ , we need to select N triplets that are disjoint, i.e. cover all elements of X, Y and Z exactly once. We convert this into a CS problem where each triplet is represented by a value which

needs to be sent from  $p_0$  to several other processors, with the concrete deadlines depending on the elements of X, Y, Z contained in the given triplet. The construction consists of two parts. The first part essentially allows us to send exactly (M-N) values from  $p_0$  to all other processors (the triplets that are not among the chosen N) within the allowed cost. The second part then allows us to send N further values from  $p_0$  to the other processors, but only if the corresponding triplets are disjoint.

Intuitively, this construction works in the DB, FS and FB models because sending a value from  $p_1$  to  $p_2$  and from  $p_1$  to  $p_3$  are not independent operations: in case of broadcast, the value sent from  $p_1$  can be directly received by both  $p_2$  and  $p_3$  at the same time, whereas in case of free data movement,  $p_1$  can send a single value to an auxiliary processor  $p_a$ , which relays this to both  $p_2$  and  $p_3$ . This property is crucial for the first part of the construction to ensure that  $p_0$  is indeed distributing the same (M-N) values to all the other processors. In contrast to this, in the DS model, the communication steps from  $p_1$  to  $p_2$  and the communication steps from  $p_1$  to  $p_3$  are essentially independent from each other, and hence the same proof strategy cannot be applied.

On the other hand, if we consider the model extension with communication weights, then it becomes relatively simple to reduce it to standard packing problems, and hence show that the problem is NP-hard already for P=2 processors.

Lemma 7.4. If we have communication weights, the communication scheduling problem is already NP-hard for P = 2.

## 8 FORMULATION AS AN ILP PROBLEM

Finally, we briefly analyze the formulations of our BSP scheduling task as an Integer Linear Programming problem. Since today's ILP solvers can often solve even relatively large instances in reasonable time, a reduction to ILP is a simple and yet effective approach for various kinds of combinatorial problems: if we formulate our problem as a reasonable-sized ILP, then ILP solvers can be used as black box to obtain optimal or near-optimal solutions. Such an ILP-based approach has provided remarkable results in several other areas, e.g. hypergraph partitioning [19].

In this section, we present a straightforward approach to formulate our BSP scheduling problem as an ILP, and we analyze the number of variables and constraints this formulation requires in the different communication models. We emphasize that the ILP formulation presented here is by no means optimal; a detailed analysis could probably make further improvements to this formulation, both in terms of size and in suitability for practical solvers. However, we believe that this simple and natural formulation provides valuable insight, both by demonstrating the easy applicability of the ILP approach, and by providing an alternative comparison method between the different models.

PROPOSITION 8.1. BSP scheduling can be formulated as an ILP problem on  $O(n \cdot P \cdot S)$  variables in the DS, DB and FB models, and on  $O(n \cdot P^2 \cdot S)$  variables in the FS model.

Proof sketch. The main idea is similar in all of the models: we introduce two binary variables  $\text{comp}_{v,p,s}$  and  $\text{pres}_{v,p,s}$  for all  $v \in V$ ,  $p \in [P]$ ,  $s \in [S]$ . The variable  $\text{comp}_{v,p,s}$  indicates whether the

The remaining variables are used to describe the communication-related costs and constraints. Regardless of the model, the communication cost can be described by a simple implementation of the variables  $C_{sent}$ ,  $C_{rec}$  and  $C_{comm}$ ; the only difference between the models is how we capture the actual communication steps.

- In broadcast models (DB and FB), we can simply add binary variables  $\mathtt{SENT}_{v,p,s}$  and  $\mathtt{REC}_{v,p,s}$  to indicate if processor p has sent or received, respectively, value v in superstep s. The linear constraints then need to ensure that if  $\mathtt{REC}_{v,p_1,s} = 1$ , then we have  $\mathtt{SEND}_{v,p_2,s} = 1$  for some other  $p_2$ , i.e. some processor is actually broadcasting the value that is received by  $p_1$ .

- In the FS model, we need to add binary variables  $\text{comm}_{v,p_1,p_2,s}$  to indicate the concrete data transfer, i.e. whether value v is being sent from processor  $p_1$  to processor  $p_2$  in superstep s; this is why the required number of variables is  $O(n \cdot P^2 \cdot S)$  in this case. The validity of the send operations here can simply be checked using the presence variables PRESv,p,s.

- Finally, in the DS model, the straightforward solution would also use the variables  $\mathsf{COMM}_{v,p_1,p_2,s}$  as in FS. However, here if node v is computed on processor p, then only processor p can send this value; with this observation and some auxiliary variables, we can also model this case with  $O(n \cdot P \cdot S)$  variables, similarly to the approach in DB and FB.

The correct interpretation of the presence variables  $PRES_{v,p,s}$  can also be ensured with a simple constraint: value v is present on processor p in superstep s if it was already present before, if it was computed in this superstep, or if it was received in the previous superstep, i.e.

$$PRES_{v,p,s} \le PRES_{v,p,(s-1)} + COMP_{v,p,s} + REC_{v,p,(s-1)}$$

in the broadcast models, for example. Finally, the precedence constraints in the DAG can also be implemented through the presence variables: if  $(u, v) \in E$ , then we need  $\text{COMP}_{v,p,s} \leq \text{PRES}_{u,p,s}$ .

The entire set of variables and linear constraints for each model is discussed in Appendix E. The number of linear constraints required is altogether  $O((n+|E|) \cdot P \cdot S)$  in the DS, DB and FB models, and  $O((n \cdot P + |E|) \cdot P \cdot S)$  in the FS model.

We point out that it is also straightforward to extend the above ILP formulation with node weights (for both work and communication), or to the case when duplication is allowed.

While the number of variables in this formulation seems rather large, it may not be prohibitive in practice with modern ILP solvers, especially for smaller DAGs. In particular, several ILP representations with a similar magnitude of variables have been suggested and analyzed in previous work for classical scheduling problems; see Appendix E for a brief overview of these. Moreover, the vast majority of variables in our formulation are binary, which can also make the solving process more efficient in practice.

#### REFERENCES

- Kenneth R Baker and Dan Trietsch. 2013. Principles of sequencing and scheduling. John Wiley & Sons.

- [2] Rob H Bisseling. 2020. Parallel Scientific Computation: A Structured Approach Using BSP. Oxford University Press, USA.

- [3] Hans L Bodlaender and Michael R Fellows. 1995. W [2]-hardness of precedence constrained k-processor scheduling. Operations Research Letters 18, 2 (1995), 93– 97

- [4] Lin Chen, Klaus Jansen, and Guochuan Zhang. 2014. On the optimality of approximation schemes for the classical scheduling problem. In Proceedings of the 25th annual ACM-SIAM symposium on Discrete algorithms (SODA). SIAM, 657– 668.

- [5] Edward G Coffman and Ronald L Graham. 1972. Optimal scheduling for twoprocessor systems. Acta informatica 1, 3 (1972), 200–213.

- [6] Danny Dolev and Manfred K Warmuth. 1984. Scheduling precedence graphs of bounded height. Journal of Algorithms 5, 1 (1984), 48–59.

- [7] Danny Dolev and Manfred K Warmuth. 1985. Profile scheduling of opposing forests and level orders. SIAM Journal on Algebraic Discrete Methods 6, 4 (1985), 665–687.

- [8] Jianzhong Du, Joseph YT Leung, and Gilbert H Young. 1991. Scheduling chainstructured tasks to minimize makespan and mean flow time. *Information and Computation* 92, 2 (1991), 219–236.

- [9] Noriyuki Fujimoto and Kenichi Hagihara. 2003. On approximation of the bulk synchronous task scheduling problem. *IEEE Transactions on Parallel and Dis*tributed Systems 14, 11 (2003), 1191–1199.

- [10] Harold N Gabow. 1982. An almost-linear algorithm for two-processor scheduling. J. ACM 29, 3 (1982), 766–780.

- [11] MR Garey, DS Johnson, RE Tarjan, and M Yannakakis. 1983. Scheduling opposing forests. SIAM Journal on Algebraic Discrete Methods 4, 1 (1983), 72–93.

- [12] M. R. Garey and D. S. Johnson. 1979. Computers and Intractability: A Guide to the Theory of NP-Completeness. W. H. Freeman.

- [13] Shashwat Garg. 2018. Quasi-PTAS for Scheduling with Precedences using LP Hierarchies. In 45th International Colloquium on Automata, Languages, and Programming (ICALP 2018). Schloss Dagstuhl-Leibniz-Zentrum fuer Informatik.

- [14] Alfredo Goldman, Gregory Mounie, and Denis Trystram. 1998. Near optimal algorithms for scheduling independent chains in BSP. In Proceedings. 5th International Conference on High Performance Computing. IEEE, 310–317.

- [15] Gaétan Hains. 1998. Subset synchronization in BSP computing. In International Conference on Parallel and Distributed Processing Techniques and Applications, Vol. 98, 242–246.

- [16] Claire Hanen and Alix Munier. 1995. An approximation algorithm for scheduling dependent tasks on m processors with small communication delays. In Proceedings 1995 INRIA/IEEE Symposium on Emerging Technologies and Factory Automation. ETFA'95, Vol. 1. IEEE, 167–189.

- [17] Jonathan MD Hill, Bill McColl, Dan C Stefanescu, Mark W Goudreau, Kevin Lang, Satish B Rao, Torsten Suel, Thanasis Tsantilas, and Rob H Bisseling. 1998. BSPlib: The BSP programming library. Parallel Comput. 24, 14 (1998), 1947–1980.

- [18] JA Hoogeveen, Jan Karel Lenstra, and Bart Veltman. 1994. Three, four, five, six, or the complexity of scheduling with communication delays. *Operations Research Letters* 16, 3 (1994), 129–137.

- [19] Engelina L Jenneskens and Rob H Bisseling. 2022. Exact k-way sparse matrix partitioning. In 2022 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW). IEEE, 754–763.

- [20] Oumar Koné, Christian Artigues, Pierre Lopez, and Marcel Mongeau. 2011. Event-based MILP models for resource-constrained project scheduling problems. Computers & Operations Research 38, 1 (2011), 3–13.

- [21] Janardhan Kulkarni, Shi Li, Jakub Tarnawski, and Minwei Ye. 2020. Hierarchy-based algorithms for minimizing makespan under precedence and communication constraints. In Proceedings of the 14th Annual ACM-SIAM Symposium on Discrete Algorithms (SODA). SIAM, 2770–2789.

- [22] Jan Karel Lenstra, AHG Rinnooy Kan, and Peter Brucker. 1977. Complexity of machine scheduling problems. In Annals of discrete mathematics. Vol. 1. Elsevier, 343–362

- [23] Jan Karel Lenstra and AHG Rinnooy Kan. 1978. Complexity of scheduling under precedence constraints. Operations Research 26, 1 (1978), 22–35.

- [24] Jan Karel Lenstra, David B Shmoys, and Éva Tardos. 1990. Approximation algorithms for scheduling unrelated parallel machines. *Mathematical programming* 46, 1 (1990), 259–271.

- [25] Joseph Y-T Leung and Gilbert H Young. 1990. Minimizing total tardiness on a single machine with precedence constraints. ORSA Journal on Computing 2, 4 (1990), 346–352.

- [26] Elaine Levey and Thomas Rothvoss. 2016. A (1+ epsilon)-approximation for makespan scheduling with precedence constraints using LP hierarchies. In Proceedings of the 48th annual ACM symposium on Theory of Computing (STOC). 168–177.

- [27] Shi Li. 2017. Scheduling to Minimize Total Weighted Completion Time via Time-Indexed Linear Programming Relaxations. In IEEE 58th Annual Symposium on

- Foundations of Computer Science (FOCS). IEEE Computer Society, 283-294.

- [28] Shi Li. 2021. Towards PTAS for Precedence Constrained Scheduling via Combinatorial Algorithms. In Proceedings of the ACM-SIAM Symposium on Discrete Algorithms (SODA). SIAM, 2991–3010.

- [29] Quanquan C Liu, Manish Purohit, Zoya Svitkina, Erik Vee, and Joshua R Wang. 2022. Scheduling with Communication Delay in Near-Linear Time. In 39th International Symposium on Theoretical Aspects of Computer Science (STACS 2022). Schloss Dagstuhl-Leibniz-Zentrum für Informatik.

- [30] Pauline Markenscoff and Yong Yuan Li. 1993. Scheduling a computational DAG on a parallel system with communication delays and replication of node execution. In Proceedings of the 7th International Parallel Processing Symposium. IEEE, 113–117

- [31] Bill McColl. 2021. Mathematics, Models and Architectures. Cambridge University Press, 6–53.

- [32] William F McColl. 1995. Scalable computing. Computer Science Today (1995), 46–61.

- [33] William F McColl and Alexandre Tiskin. 1999. Memory-efficient matrix multiplication in the BSP model. Algorithmica 24, 3 (1999), 287–297.

- [34] Matthias Mnich and Andreas Wiese. 2015. Scheduling and fixed-parameter tractability. Mathematical Programming 154, 1 (2015), 533–562.

- [35] Alix Munier and Jean-Claude König. 1997. A heuristic for a scheduling problem with communication delays. Operations Research 45, 1 (1997), 145–147.

- [36] M. Yusuf Özkaya, Anne Benoit, Bora Uçar, Julien Herrmann, and Ümit V. Çatalyürek. 2019. A Scalable Clustering-Based Task Scheduler for Homogeneous Processors Using DAG Partitioning. In IEEE International Parallel and Distributed Processing Symposium (IPDPS). IEEE, 155–165.

- [37] Christos Papadimitriou and Mihalis Yannakakis. 1988. Towards an architecture-independent analysis of parallel algorithms. In *Proceedings of the 20th annual ACM symposium on Theory of computing (STOC)*. 510–513.

[38] Pál András Papp, Georg Anegg, and A. N. Yzelman. 2022. Partitioning Hyper-

- [38] Pál András Papp, Georg Anegg, and A. N. Yzelman. 2022. Partitioning Hypergraphs is Hard: Models, Inapproximability, and Applications. arXiv preprint arXiv:2208.08257.

- [39] Merten Popp, Sebastian Schlag, Christian Schulz, and Daniel Seemaier. 2021. Multilevel Acyclic Hypergraph Partitioning. In Proceedings of the Symposium on Algorithm Engineering and Experiments (ALENEX). 1–15.

- [40] J Roda, Casiano Rodriguez, DG Morales, and Francisco Almeida. 1998. Bulk synchronous parallel without barriers. In Proceedings. 24th EUROMICRO Conference, Vol. 2. IEEE. 961–968.

- [41] Peter Sanders, Kurt Mehlhorn, Martin Dietzfelbinger, and Roman Dementiev. 2019. Sequential and Parallel Algorithms and Data Structures. Springer.

- [42] Ravi Sethi. 1976. Scheduling graphs on two processors. SIAM J. Comput. 5, 1 (1976), 73–82.

- [43] David B Skillicorn, Jonathan Hill, and William F McColl. 1997. Questions and answers about BSP. Scientific Programming 6, 3 (1997), 249–274.

- [44] Ola Svensson. 2010. Conditional hardness of precedence constrained scheduling on identical machines. In Proceedings of the 42nd ACM symposium on Theory of computing (STOC). 745–754.

- [45] Vadim G Timkovsky. 2003. Identical parallel machines vs. unit-time shops and preemptions vs. chains in scheduling complexity. European Journal of Operational Research 149, 2 (2003), 355–376.

- [46] Jeffrey D. Ullman. 1975. NP-complete scheduling problems. Journal of Computer and System sciences 10, 3 (1975), 384–393.

- [47] Leslie G Valiant. 1990. A bridging model for parallel computation. Commun. ACM 33, 8 (1990), 103–111.

- [48] Leslie G Valiant. 2008. A bridging model for multi-core computing. In European Symposium on Algorithms (ESA). Springer, 13–28.

- [49] Leslie G Valiant. 2011. A bridging model for multi-core computing. J. Comput. System Sci. 77, 1 (2011), 154–166.

- [50] Bart Veltman, BJ Lageweg, and Jan Karel Lenstra. 1990. Multiprocessor scheduling with communication delays. *Parallel computing* 16, 2-3 (1990), 173–182.

- [51] AN Yzelman and Rob H Bisseling. 2012. An object-oriented bulk synchronous parallel library for multicore programming. Concurrency and Computation: Practice and Experience 24, 5 (2012), 533–553.

- [52] AN Yzelman, Rob H Bisseling, Dirk Roose, and Karl Meerbergen. 2014. MulticoreBSP for C: a high-performance library for shared-memory parallel programming. *International Journal of Parallel Programming* 42, 4 (2014), 619–642.

# A DETAILED DEFINITION OF DIFFERENT MODEL VARIANTS

We first give a more formal definition of the numerous scheduling models that were analyzed (or only briefly mentioned) in the paper. Note that besides BSP, the simplest scheduling models from the literature (classical scheduling and commdelay) were already defined in Section 4.1.

We begin with the alternative communication models within BSP (the DB, FS and FB models), since these play a central role in our theoretical results in Sections 7 and 8. We then continue with the remaining models that are only loosely related to BSP.

## A.1 DB, FS and FB models

To define the BSP scheduling problem with broadcast communication (and hence switch from our initial definition of the DS model to DB), we need to redefine the send cost  $C_{sent}$  (s,p) as

$$C_{sent}(s,p) = |\{v \in V \mid \exists p' \in [P] \text{ such that } (v,p,p',s) \in \Gamma\}|,$$

while the rest of the definitions remain unchanged.

To allow free movement of data (switch from the DS model to FS), we need to introduce auxiliary variables similarly to the PRESv,p,s variables in the ILP formulation; to avoid confusion, we develop a different notation for these in this context, referring to them as  $\mu(v,p,s)$ . Formally, we let the auxiliary variable  $\mu(v,p,s) \in \{0,1\}$  indicate whether the output of v is already present on processor p at the end of the computational phase of superstep s; that is, we have  $\mu(v,p,s)=1$  if either  $\pi(v)=p$  and  $\tau(v)\leq s$ , or if there is a  $(v,p'p,s')\in\Gamma$  with s'< s. In the validity conditions of Section 3.1.2, Condition (i) will now require for all  $(u,v)\in E$  to have  $\mu(u,\pi(v),\tau(v))=1$ , and Condition (ii) will state that if  $(v,p_1,p_2,s)\in\Gamma$ , then we must have  $\mu(v,p_1,s)=1$ .

Note that the modified definition for broadcasting and for free data movement can be combined in a straightforward way to obtain the definition of the FB model, since the corresponding modifications affect different aspects of the model definition anyway.

## A.2 Single-port duplex model

The SPD model has been studied in the work of [36]; we slightly change this definition to adapt it to node-based communication.

Similarly to commdelay, an SPD schedule has a constant parameter g, and consists of an assignment  $\pi:V\to [P]$  and  $t:V\to \mathbb{Z}^+$ , but also a communication schedule  $\Gamma\subset V\times [P]\times [P]\times \mathbb{Z}^+$ , where  $(v,p_1,p_2,t_0)\in\Gamma$  describes that value v is sent from  $p_1$  to  $p_2$  at time step  $t_0$ . These communication steps in  $\Gamma$  must satisfy two conditions for validity: the values that are sent must already be computed (i.e. if  $(v,p_1,p_2,t_0)\in\Gamma$  then  $t(v)\leq t_0$ ), and each processor can only send and receive a single value at a given time (i.e. if  $(v_1,p_1,p_2,t_1),(v_2,p_{1,2},p_{2,2},t_2)\in\Gamma$  and the intervals  $(t_1,t_1+g]$  and  $(t_2,t_2+g]$  are not disjoint, then we must have  $p_{1,1}\neq p_{1,2}$  and  $p_{2,1}\neq p_{2,2}$ ).

For a correct SPD schedule, we still require that a processor only computes a single node at a time  $(\nexists u, v \in V \text{ with } \pi(u) = \pi(v), t(u) = t(v))$ . For all  $(u, v) \in E$ , if  $\pi(u) = \pi(v)$ , then we still need to have t(u) < t(v). For edges  $(u, v) \in E \text{ with } \pi(u) \neq \pi(v)$ , we require that there is a  $(u, \pi(u), \pi(v), t_0) \in \Gamma \text{ with } t_0 + g < t(v)$ . As before, the cost of a schedule is simply its makespan  $\max_{v \in V} t(v)$ .

#### A.3 MaxBSP

As discussed in Section 4, the reasonable interpretation of maxBSP to DAG scheduling is to assume that every superstep contains a simultaneous computation and communication phase. To achieve this, we only need minor modifications in the original BSP definition. In particular, in validity condition (ii), we need to require that if  $(v, p_1, p_2, s) \in \Gamma$ , then besides  $p_1 = \pi(v)$ , we must have  $\tau(v) < s$  with strict inequality, since the communication phase of s now overlaps with its computation phase. Besides this, we simply need to adjust the cost of a superstep. One possible choice for this is

$$C^{(s)} = \max \left( C_{work}^{(s)} , g \cdot C_{comm}^{(s)} + L \right),$$

but as a natural alternative, we could also have

$$C^{(s)} = \max \left( C_{work}^{(s)}, g \cdot C_{comm}^{(s)} \right) + L.$$

## A.4 The $\alpha - \beta$ model and subset-BSP

The third cell in the last column of Table 2 can be interpreted in several different ways for DAG scheduling; below we discuss two of these. The main difference between these two variants is whether they require subset synchronization between the nodes that are currently communicating, similarly to how BSP requires it between all processors. That is, one natural interpretation of this setting is what we call subset-BSP, where the schedule is still divided into computation and communication phases, just like BSP, but the different processors can decide to do these communication phases at separate points in time: each such communication phase can happen only between a given subset of processors, while the rest of the processors keep computing in the meantime. The other natural interpretation is closer to the spirit of the  $\alpha - \beta$  model (with  $\alpha = 0$ ), where no synchronization is required at all; in other words, this is essentially identical to the SPD model, with the minor difference that while communicating, a processor is unable to compute.

To demonstrate the difference between these two models, assume for instance that  $p_1$  computes a value  $v_1$  in time step  $t_0$ , and wants to send this to  $p_2$  in the time interval  $(t_0, t_0 + g]$ , while  $p_3$  computes another value  $v_2$  in time step  $t_0 + 1$ , and wants to send this to  $p_1$  in the time interval  $(t_0 + 1, t_0 + g + 1]$ . This does not violate any condition in the  $\alpha - \beta$  model, but it is not allowed in subset-BSP, since  $p_3$  is not yet finished with the computation of  $v_2$  at  $t_0$ , so it cannot begin a communication phase together with  $p_1$  at this point.

We first begin with the definition of the  $\alpha-\beta$  model, since this is surprisingly simple. We can simply take the definition of the SPD model, and extend it with a simple further condition on validity: if there is a communication step  $(u,p_1,p_2,t_0)\in \Gamma$ , then we cannot have any  $v\in V$  such that  $\pi(v)\in \{p_1,p_2\}$  and  $t_0<\tau(v)\leq t_0+g$ . We once again point out that since the  $\alpha-\beta$  model is mostly used as a cost function and not a complete model in the related work, this is just one possible interpretation of it; some other works assume e.g. that a processor is not even allowed to send and receive at the same time, which would make this setting significantly different from all other models in our taxonomy.

On the other hand, formally defining the subset-BSP scheduling model much more technical. For convenience, we modify the definition of supersteps for this, and assume that each superstep